# **DNx-MF-101 User Manual**

Multifunction I/O Board for the PowerDNA Cube and RACK Series Chassis

**March 2025**

PN Man-DNx-MF-101

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form by any means, electronic, mechanical, by photocopying, recording, or otherwise without prior written permission.

Information furnished in this manual is believed to be accurate and reliable. However, no responsibility is assumed for its use, or for any infringement of patents or other rights of third parties that may result from its use.

All product names listed are trademarks or trade names of their respective companies.

$\epsilon$

#### **Contacting United Electronic Industries**

Mailing Address:Shipping Address:249 Vanderbilt Avenue24 Morgan DriveNorwood, MA 02062Norwood, MA 02062

U.S.A. U.S.A.

For a list of our distributors and partners in the US and around the world, please contact a member of our support team:

Support:

Telephone: (508) 921-4600 Fax: (508) 668-2350

Also see the FAQs and online "Live Help" feature on our web site.

Internet Support:

Support: <u>uei.support@ametek.com</u>

Website: www.ueidag.com

#### **Product Disclaimer:**

#### **WARNING!**

### DO NOT USE PRODUCTS SOLD BY UNITED ELECTRONIC INDUSTRIES, INC. AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

Products sold by United Electronic Industries / AMETEK are not authorized for use as critical components in life support devices or systems. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Any attempt to purchase any United Electronic Industries / AMETEK product for that purpose is null and void and United Electronic Industries / AMETEK accepts no liability whatsoever in contract, tort, or otherwise whether or not resulting from our or our employees' negligence or failure to detect an improper purchase.

Specifications in this document are subject to change without notice. Check with UEI for current status.

### **Table of Contents**

| Chapter                                                                              | 1 Introduction                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                  | Organization of this Manual                                                                                                                                                                                                                                    |

| 1.2                                                                                  | Manual Conventions                                                                                                                                                                                                                                             |

| 1.3                                                                                  | Naming Conventions                                                                                                                                                                                                                                             |

| 1.4                                                                                  | Related Resources                                                                                                                                                                                                                                              |

| 1.5                                                                                  | Before You Begin                                                                                                                                                                                                                                               |

| 1.6<br>1.6.1<br>1.6.2<br>1.6.3<br>1.6.4<br>1.6.5<br>1.6.6<br>1.6.7<br>1.6.8<br>1.6.9 | DNx-MF-101 Features Analog Input Analog Output Digital I/O Communication Ports Guardian Diagnostics Isolation & Over-voltage Protection Environmental Conditions Accessories Software Support                                                                  |

| 1.7<br>1.7.1<br>1.7.2<br>1.7.3<br>1.7.4<br>1.7.5<br>1.7.6<br>1.7.7                   | Technical Specifications       Analog Input         Analog Output       8         Industrial Digital I/O       9         TTL Digital I/O       9         Counter/Timer       10         Serial Port       10         I2C Port       10         General       1 |

| Chapter                                                                              | 2 I/O Functional Descriptions                                                                                                                                                                                                                                  |

| 2.1<br>2.1.1                                                                         | Analog Input                                                                                                                                                                                                                                                   |

| 2.2<br>2.2.1                                                                         | Analog Output                                                                                                                                                                                                                                                  |

| 2.3<br>2.3.1<br>2.3.2<br>2.3.3                                                       | Digital I/O       14         Industrial Digital I/O       15         TTL Digital I/O       17         Counters       17                                                                                                                                        |

| 2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5                                     | Serial Port       2         What is a Serial Port?       2         Serial Transactions       2         Minor and Major Frames       2         Flow Control       2         Loopback Diagnostics       2                                                        |

| 2.5<br>2.5.1<br>2.5.2<br>2.5.3                                                       | I2C Port       24         About I2C Transactions       24         Master Module       25         Slave Module       26                                                                                                                                         |

| 2.5.4                                            | Loopback Testing                                                                                                                          | 28             |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.6                                              | Indicators and Connectors                                                                                                                 | 26             |

| 2.7                                              | Pinout                                                                                                                                    | 30             |

| 2.8<br>2.8.1<br>2.8.2<br>2.8.3<br>2.8.4          | Wiring Guidelines Analog Input Wiring Industrial Digital Output Wiring Serial Port Wiring I2C Port Wiring                                 | 32<br>33<br>34 |

| Chapter                                          | 3 PowerDNA Explorer                                                                                                                       | 37             |

| 3.1                                              | Introduction                                                                                                                              |                |

| 3.2<br>3.2.1<br>3.2.2                            | Analog Input                                                                                                                              | 39<br>39       |

| 3.3<br>3.3.1<br>3.3.2                            | Analog Output                                                                                                                             | 41             |

| 3.4                                              | Industrial Digital Input                                                                                                                  | 43             |

| 3.5<br>3.5.1<br>3.5.2                            | Industrial Digital Output                                                                                                                 | 45             |

| 3.6<br>3.6.1<br>3.6.2                            | RS-232/422/485 Port       4         Configure Serial Port       4         Send/Receive Data       4                                       | 48             |

| 3.7<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4          | I2C Port                                                                                                                                  | 51<br>52<br>53 |

| 3.8<br>3.8.1<br>3.8.2<br>3.8.3<br>3.8.4<br>3.8.5 | Counter/Timer                                                                                                                             | 56<br>57<br>58 |

| 3.9<br>3.9.1<br>3.9.2<br>3.9.3                   | Logic-Level DIO.         6           Configure TTL Port.         6           Read TTL Port.         6           Write TTL Data.         6 | 31<br>32       |

| Chapter                                          | 4 Programming with High-level API                                                                                                         | 34             |

| 4.1                                              | About the High-level API                                                                                                                  | 34             |

| 4.2                                              | Example Code                                                                                                                              | 35             |

| 4.3                                              | Create a Session                                                                                                                          | 35             |

| 4.4                                              | Assemble the Resource String                                                                                                              | 35             |

| 4.5                                              | Configure the Timing                                                                                                     | 68                   |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.6                                              | Start the Session                                                                                                        | 69                   |

| 4.7<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>4.7.5 | Analog Input Session.  Add Input Channels  Enable Voltage Divider.  Add Timestamp.  Configure Moving Average  Read Data. | 69<br>70<br>70<br>70 |

| 4.8<br>4.8.1<br>4.8.2<br>4.8.3                   | Analog Output Session                                                                                                    | 71<br>72             |

| 4.9<br>4.9.1<br>4.9.2<br>4.9.3                   | Industrial Digital Input Session  Configure Input Channels  Read Data  Read Input Voltages                               | 73<br>74             |

| 4.10<br>4.10.1<br>4.10.2<br>4.10.3               | Industrial Digital Output Session                                                                                        | 75<br>78             |

| 4.11<br>4.11.1<br>4.11.2                         | TTL Digital Input Session  Configure Input Port  Read Data.                                                              | 78                   |

| 4.12<br>4.12.1<br>4.12.2                         | TTL Digital Output Session                                                                                               | 79                   |

| 4.13<br>4.13.1<br>4.13.2<br>4.13.3<br>4.13.4     | Counter Input Session                                                                                                    | 80<br>80<br>81       |

| 4.14<br>4.14.1<br>4.14.2<br>4.14.3<br>4.14.4     | Counter Output Session  Add Output Channels  Route Counter to DIO Pins  Counter Output Modes  Write Output Parameters    | 83<br>83<br>83       |

| 4.15<br>4.15.1<br>4.15.2                         | Diagnostics Session                                                                                                      | 85                   |

| 4.16<br>4.16.1<br>4.16.2<br>4.16.3               | Serial Port Session                                                                                                      | 87<br>89             |

| 4.17<br>4.17.1<br>4.17.2<br>4.17.3               | I2C Port Session                                                                                                         | 90<br>91             |

| 4.17.4                                           | Write Data                                                               | 94                         |

|--------------------------------------------------|--------------------------------------------------------------------------|----------------------------|

| 4.18                                             | Stop the Session                                                         | 94                         |

| Chapte                                           | er 5 Programming with Low-level API                                      | 96                         |

| 5.1                                              | About the Low-level API                                                  | 96                         |

| 5.2                                              | Example Code                                                             | 96                         |

| 5.3<br>5.3.1                                     | Data Acquisition Modes                                                   |                            |

| 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5 | Point-by-Point API Analog I/O Digital I/O Counters Serial Port I2C Port. | 98<br>99<br>. 100<br>. 102 |

| 5.5                                              | Async Events API                                                         | . 107                      |

| 5.6<br>5.6.1                                     | RtDMap APIDMap Tutorial                                                  |                            |

| 5.7<br>5.7.1                                     | RtVMap API (Analog IO)                                                   |                            |

| 5.8<br>5.8.1                                     | RtVMap API (Serial)                                                      |                            |

| 5.9<br>5.9.1                                     | AVMap API                                                                |                            |

| <b>Appen</b><br>A.1<br>A.2                       | dix A Accessories                                                        | . 121                      |

| A 3                                              | Test Adapter                                                             | 124                        |

### **List of Figures**

| Onapter                                                                                                                                                     | 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Chapter                                                                                                                                                     | 2 I/O Functional Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                    |

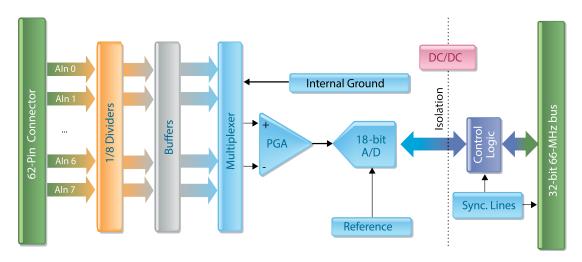

| 2-1                                                                                                                                                         | Block Diagram of DNx-MF-101 Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |

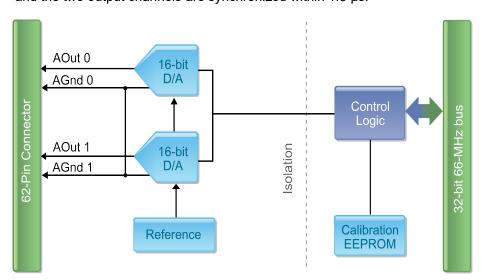

| 2-2                                                                                                                                                         | Block Diagram of DNx-MF-101 Analog Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                       |

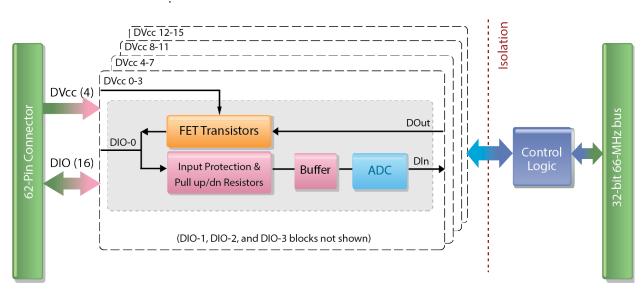

| 2-3                                                                                                                                                         | Block Diagram of DNx-MF-101 Industrial Digital I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |

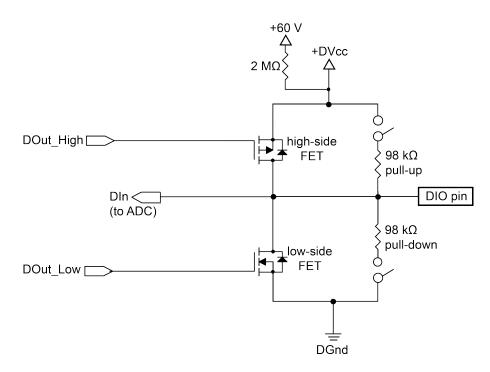

| 2-4                                                                                                                                                         | Simplified Circuit Diagram of an Industrial DIO Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       |

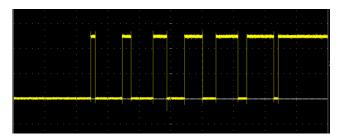

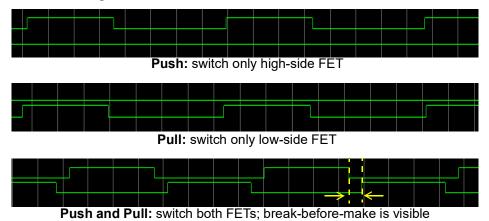

| 2-5                                                                                                                                                         | Typical PWM Soft Start cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                       |

| 2-6                                                                                                                                                         | PWM Push/Pull output modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       |

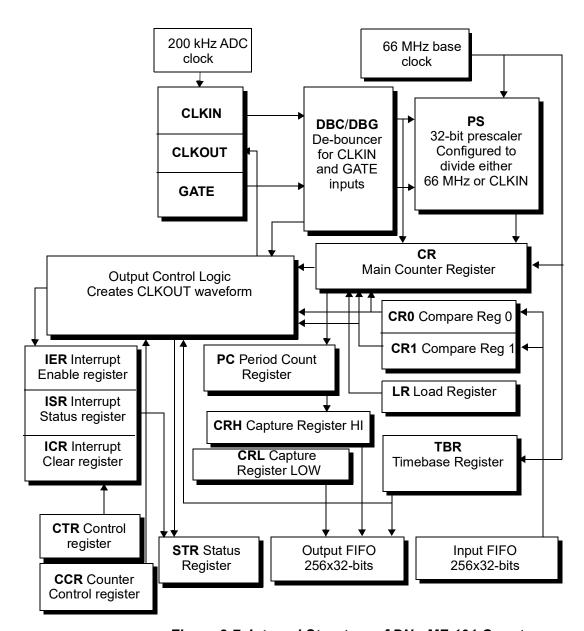

| 2-7                                                                                                                                                         | Internal Structure of DNx-MF-101 Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |

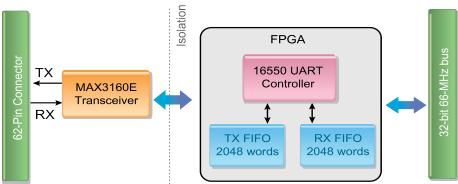

| 2-8                                                                                                                                                         | Block Diagram of DNx-MF-101 Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                                                    |

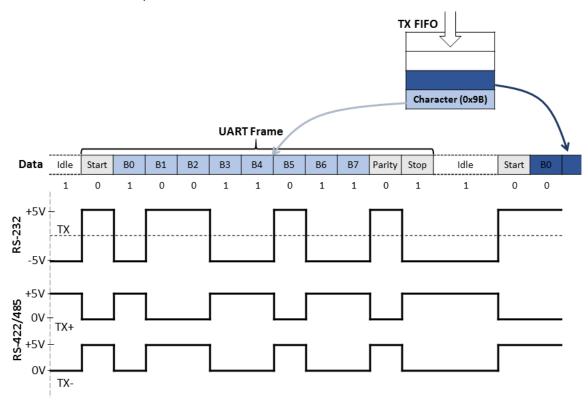

| 2-9                                                                                                                                                         | Example of Serial Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                    |

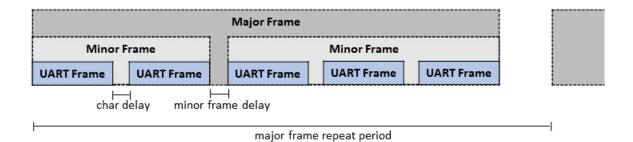

| 2-10                                                                                                                                                        | Major Frame with Variable-length Minor Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                                    |

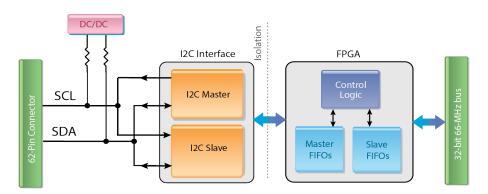

| 2-11                                                                                                                                                        | Block Diagram of DNx-MF-101 I2C Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                    |

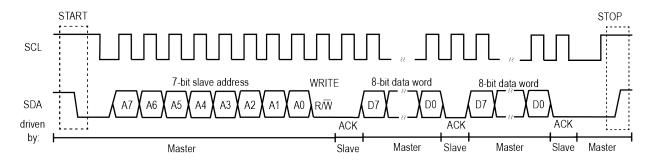

| 2-12                                                                                                                                                        | I2C Master Writing Two Bytes(7-bit Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24                                                    |

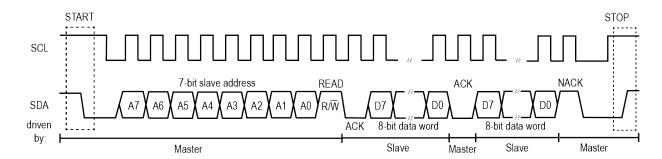

| 2-13                                                                                                                                                        | I2C Master Reading Two Bytes (7-bit Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                       |

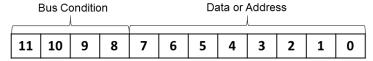

| 2-14                                                                                                                                                        | Slave RX Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |

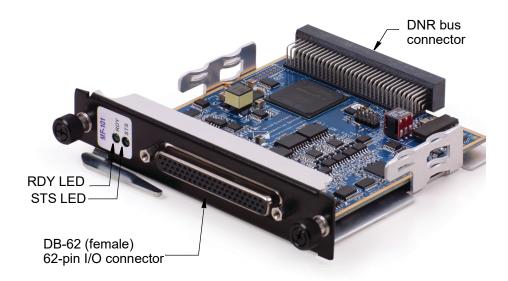

| 2-15                                                                                                                                                        | Photo of DNR-MF-101 Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                       |

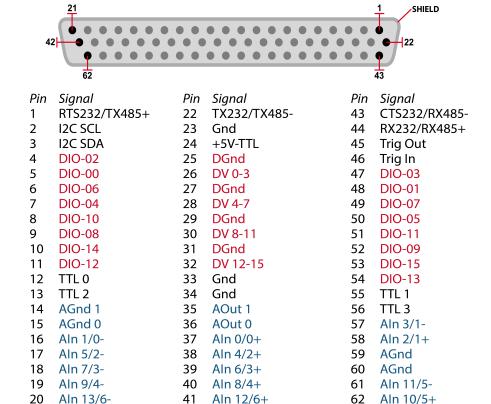

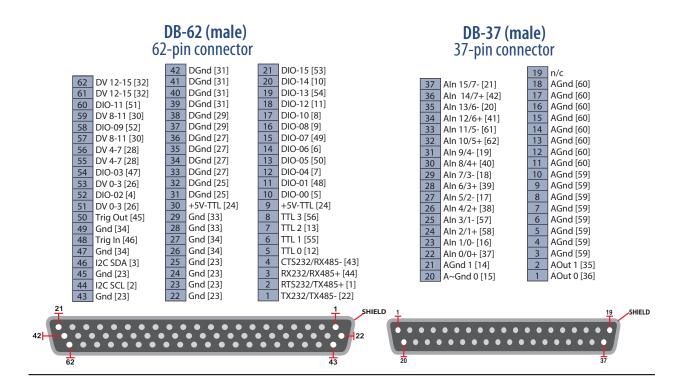

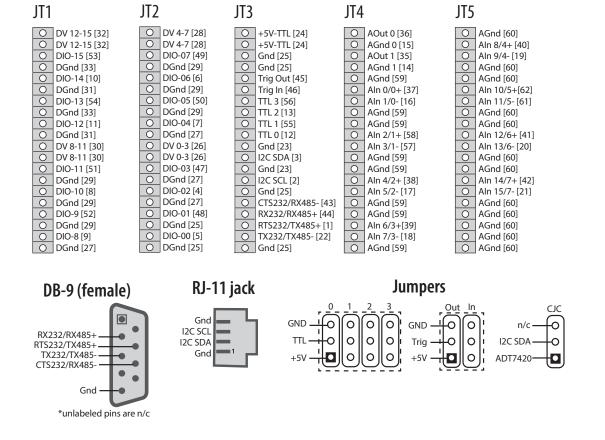

| 2-16                                                                                                                                                        | Pinout Diagram for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |

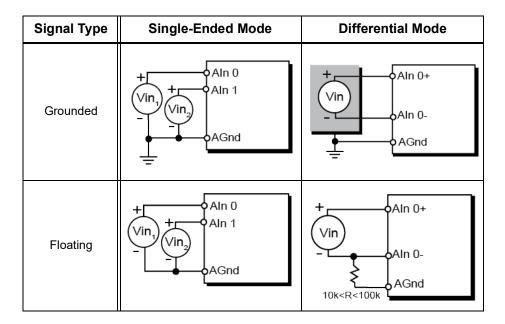

| 2-17                                                                                                                                                        | Analog Input Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |

| 2-18                                                                                                                                                        | Improper Analog Input Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                       |

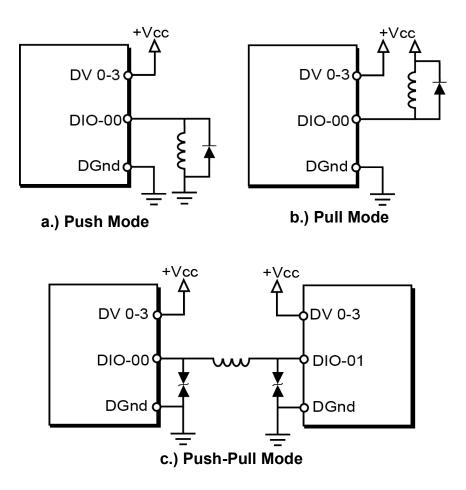

| 2-19                                                                                                                                                        | Industrial Digital Output Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

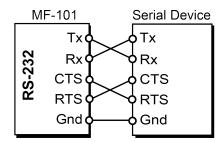

| 2-20                                                                                                                                                        | RS-232 Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |

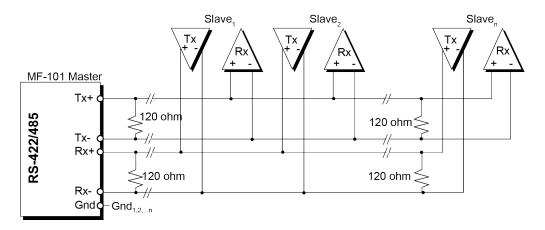

| 2-21                                                                                                                                                        | RS-422 and RS-485 Full Duplex Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |

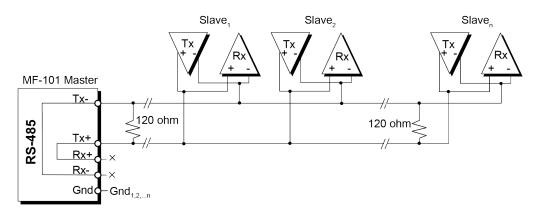

| 2-22                                                                                                                                                        | RS-485 Half Duplex Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                       |

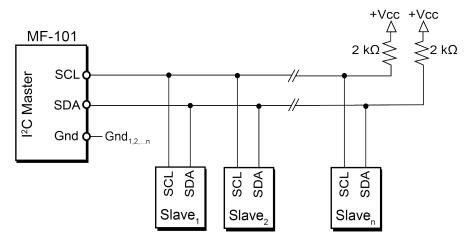

| 2-23                                                                                                                                                        | I2C Wiring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36                                                    |

|                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |

| Chapter                                                                                                                                                     | 3 PowerDNA Explorer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                    |

| Chapter 3-1                                                                                                                                                 | <b>3 PowerDNA Explorer</b> PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                       |

| -                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38                                                    |

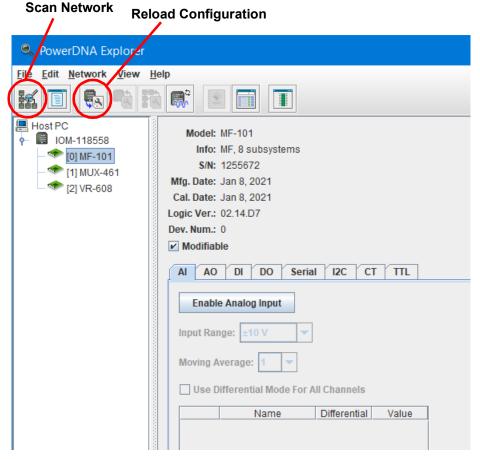

| 3-1                                                                                                                                                         | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38<br>40                                              |

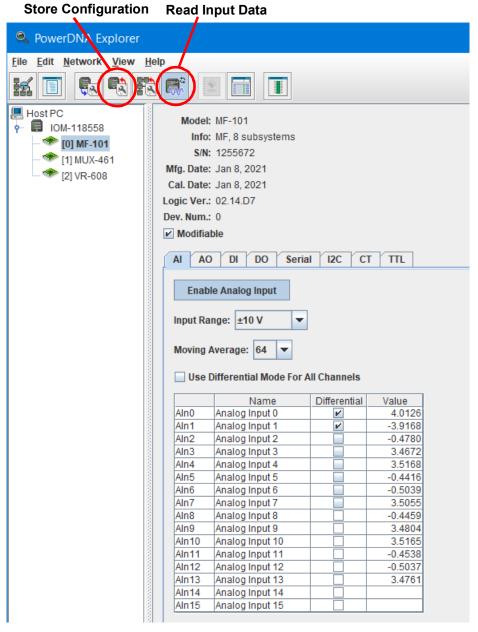

| 3-1<br>3-2                                                                                                                                                  | PowerDNA Explorer for DNx-MF-101 PowerDNA Explorer AI Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38<br>40<br>41                                        |

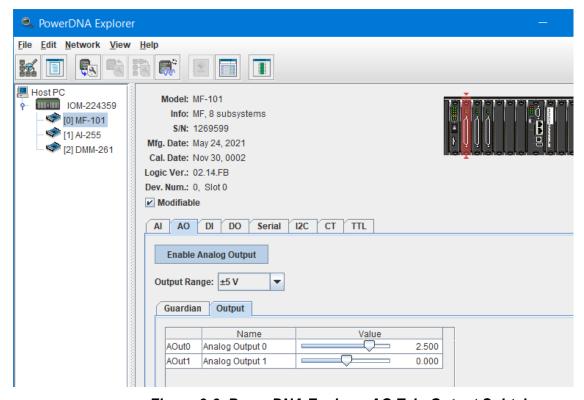

| 3-1<br>3-2<br>3-3                                                                                                                                           | PowerDNA Explorer for DNx-MF-101  PowerDNA Explorer AI Tab  PowerDNA Explorer AO Tab, Output Subtab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38<br>40<br>41                                        |

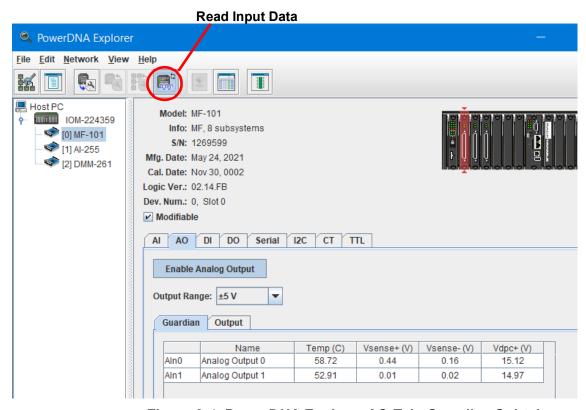

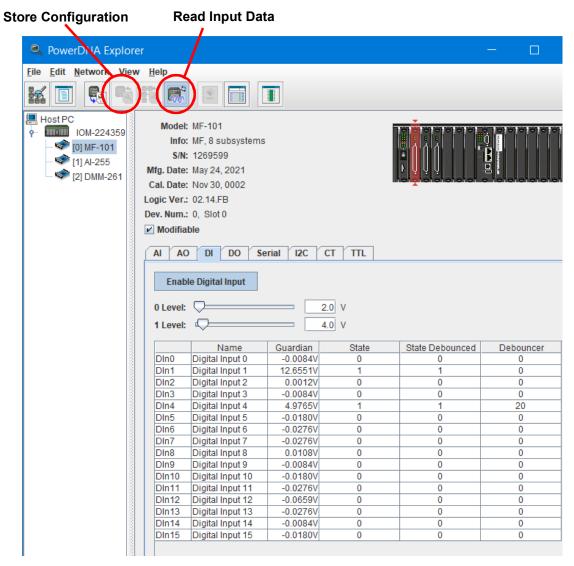

| 3-1<br>3-2<br>3-3<br>3-4                                                                                                                                    | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

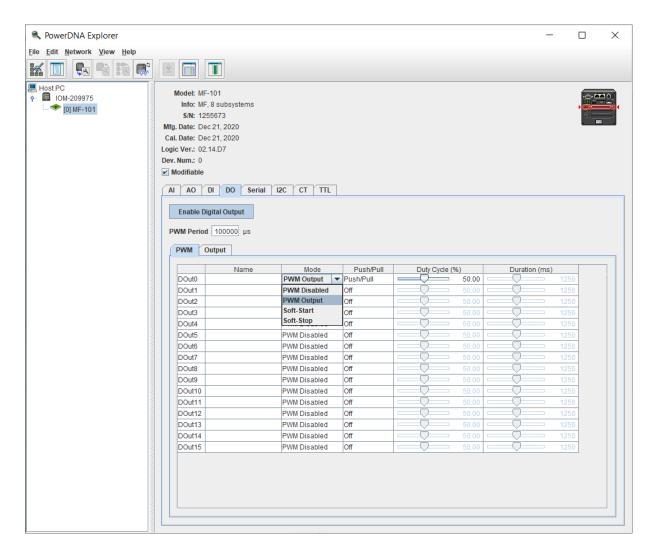

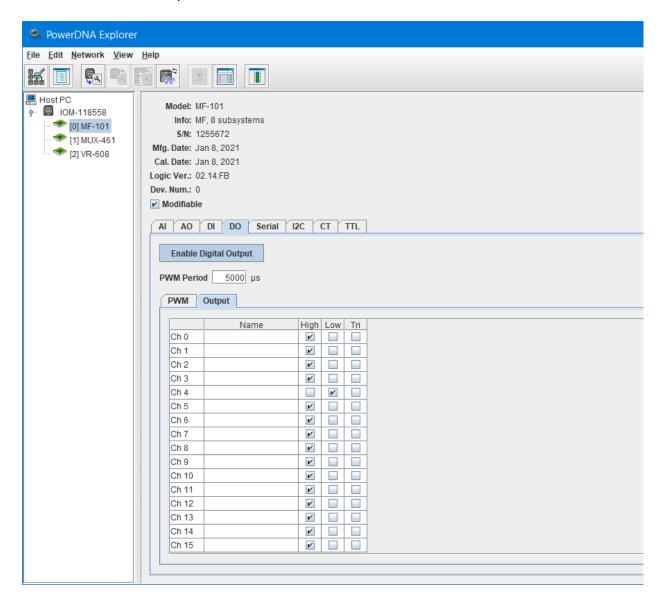

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5                                                                                                                             | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6                                                                                                                      | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

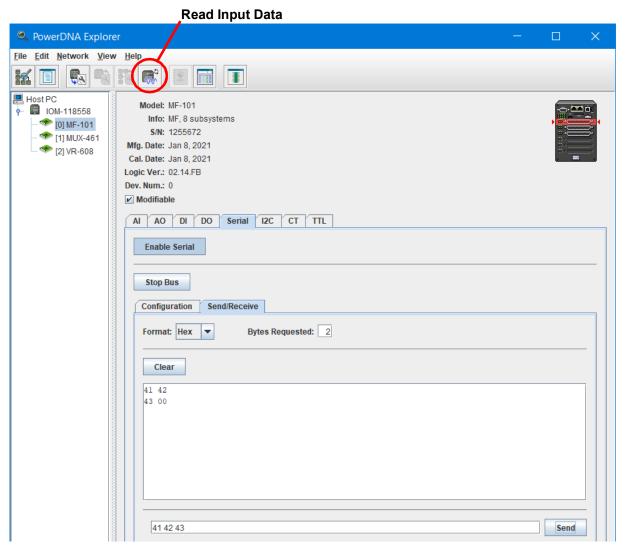

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7                                                                                                               | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

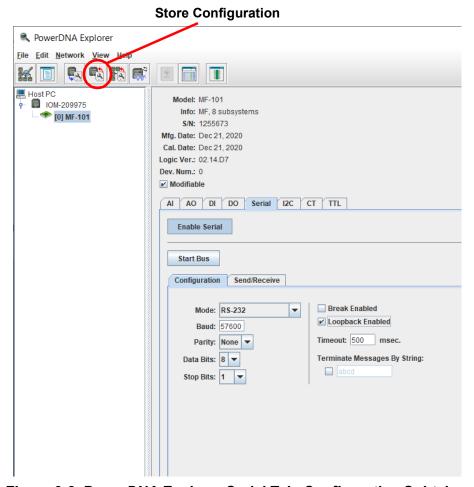

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8                                                                                                        | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

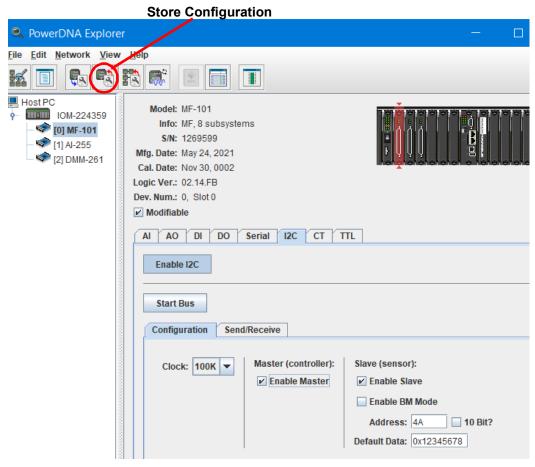

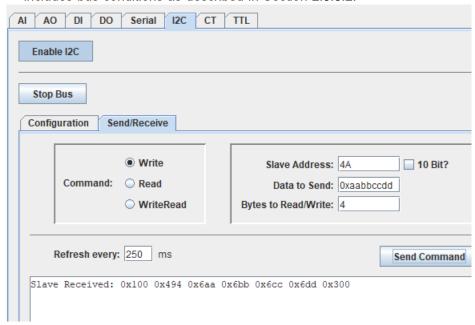

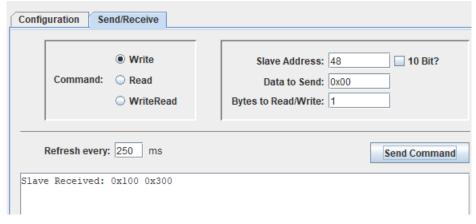

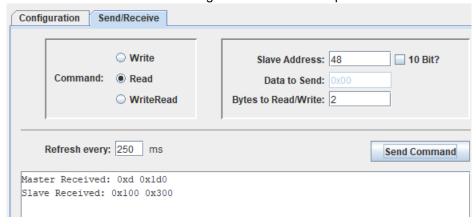

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9                                                                                                 | PowerDNA Explorer for DNx-MF-101  PowerDNA Explorer AI Tab  PowerDNA Explorer AO Tab, Output Subtab  PowerDNA Explorer AO Tab, Guardian Subtab  PowerDNA Explorer DI Tab  PowerDNA Explorer DO Tab, PWM Subtab  PowerDNA Explorer DO Tab, Output Subtab  PowerDNA Explorer Serial Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Send/Receive Subtab  PowerDNA Explorer I2C Tab, Configuration Subtab  PowerDNA Explorer I2C Tab, Configuration Subtab  Write Slave FIFO Command                                                                                                                                                                                                                                                                                                              |                                                       |

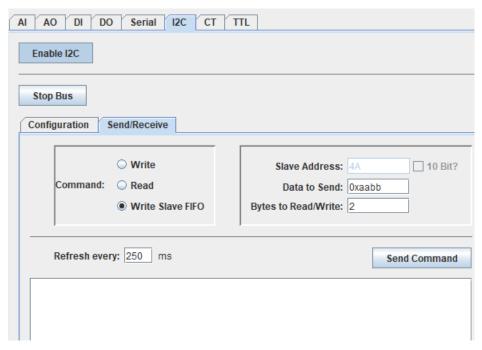

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12                                                                         | PowerDNA Explorer for DNx-MF-101  PowerDNA Explorer AI Tab  PowerDNA Explorer AO Tab, Output Subtab  PowerDNA Explorer AO Tab, Guardian Subtab  PowerDNA Explorer DI Tab  PowerDNA Explorer DO Tab, PWM Subtab  PowerDNA Explorer DO Tab, Output Subtab  PowerDNA Explorer Serial Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Send/Receive Subtab  PowerDNA Explorer I2C Tab, Configuration Subtab  Write Slave FIFO Command  Read Command                                                                                                                                                                                                                                                                                                                                                 |                                                       |

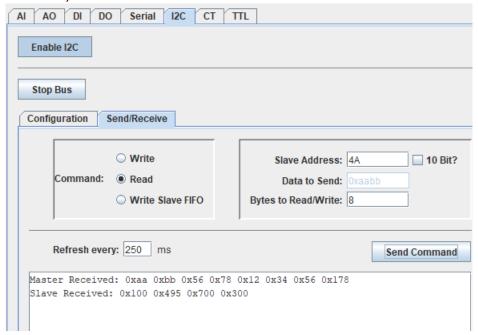

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13                                                                 | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14                                                         | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15                                                 | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 40 41 42 44 46 47 50 51 52 53 54 54                |

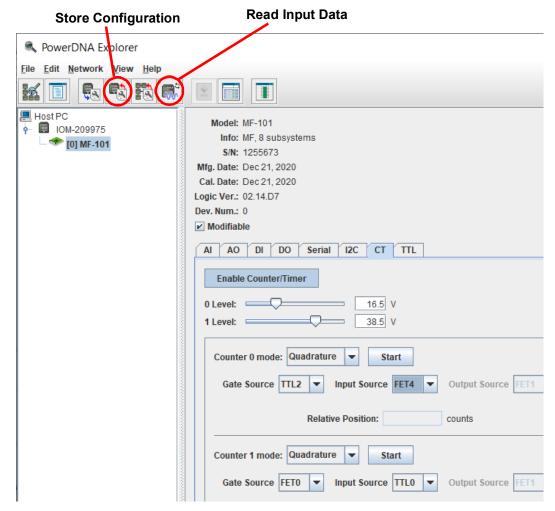

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16                                         | PowerDNA Explorer for DNx-MF-101  PowerDNA Explorer AO Tab, Output Subtab  PowerDNA Explorer AO Tab, Guardian Subtab  PowerDNA Explorer DI Tab  PowerDNA Explorer DO Tab, PWM Subtab  PowerDNA Explorer DO Tab, Output Subtab  PowerDNA Explorer DO Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Send/Receive Subtab  PowerDNA Explorer I2C Tab, Configuration Subtab  Write Slave FIFO Command  Read Command  Read Command  Setup Address for Temperature Sensor  Send Command to Read Temperature Sensor  PowerDNA Explorer CT Tab, Quadrature Mode                                                                                                                                                                                   | 38 40 41 42 44 46 47 50 51 52 53 54 55 57             |

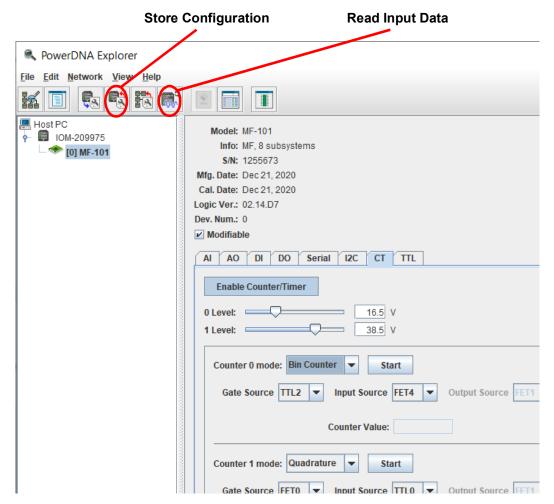

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17                                 | PowerDNA Explorer for DNx-MF-101  PowerDNA Explorer AI Tab  PowerDNA Explorer AO Tab, Output Subtab  PowerDNA Explorer DI Tab  PowerDNA Explorer DI Tab  PowerDNA Explorer DO Tab, PWM Subtab  PowerDNA Explorer DO Tab, Output Subtab  PowerDNA Explorer Serial Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Send/Receive Subtab  PowerDNA Explorer I2C Tab, Configuration Subtab  Write Slave FIFO Command  Read Command  Write Command  Setup Address for Temperature Sensor  Send Command to Read Temperature Sensor  PowerDNA Explorer CT Tab, Quadrature Mode  PowerDNA Explorer CT Tab, Bin Counter Mode                                                                                                                                                                             | 38 40 41 42 44 46 47 50 51 52 53 54 55 55 57          |

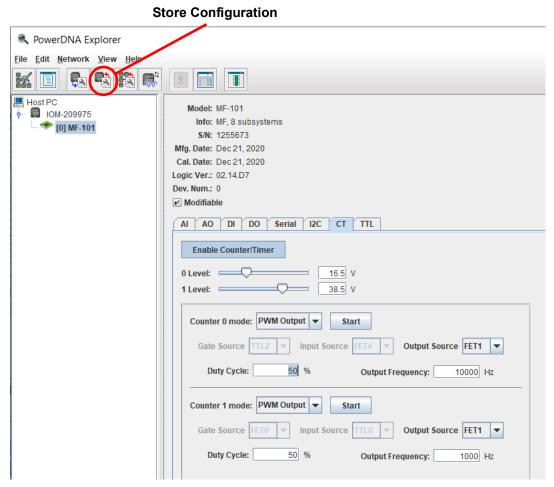

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18                         | PowerDNA Explorer for DNx-MF-101  PowerDNA Explorer AO Tab, Output Subtab  PowerDNA Explorer AO Tab, Guardian Subtab  PowerDNA Explorer DI Tab  PowerDNA Explorer DO Tab, PWM Subtab  PowerDNA Explorer DO Tab, Output Subtab  PowerDNA Explorer DO Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Send/Receive Subtab  PowerDNA Explorer I2C Tab, Configuration Subtab  Write Slave FIFO Command  Read Command  Write Command  Setup Address for Temperature Sensor  Send Command to Read Temperature Sensor  PowerDNA Explorer CT Tab, Quadrature Mode  PowerDNA Explorer CT Tab, Bin Counter Mode  PowerDNA Explorer CT Tab, PWM Output Mode                                                                                           |                                                       |

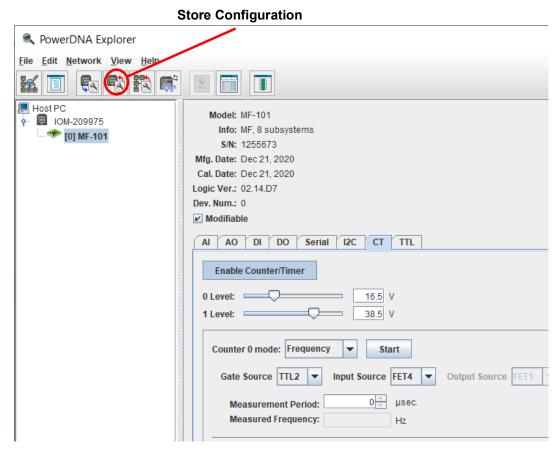

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19                 | PowerDNA Explorer for DNx-MF-101  PowerDNA Explorer AI Tab  PowerDNA Explorer AO Tab, Output Subtab  PowerDNA Explorer AO Tab, Guardian Subtab  PowerDNA Explorer DI Tab  PowerDNA Explorer DO Tab, PWM Subtab  PowerDNA Explorer DO Tab, Output Subtab  PowerDNA Explorer Serial Tab, Configuration Subtab  PowerDNA Explorer Serial Tab, Send/Receive Subtab  PowerDNA Explorer I2C Tab, Configuration Subtab  Write Slave FIFO Command  Read Command  Write Command  Setup Address for Temperature Sensor  Send Command to Read Temperature Sensor  PowerDNA Explorer CT Tab, Quadrature Mode  PowerDNA Explorer CT Tab, Bin Counter Mode  PowerDNA Explorer CT Tab, PWM Output Mode  PowerDNA Explorer CT Tab, Frequency Mode                                                                       |                                                       |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>3-20         | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 40 41 42 44 46 47 50 51 52 53 54 54 55 57 58 60 61 |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>3-20<br>3-21 | PowerDNA Explorer for DNx-MF-101 PowerDNA Explorer Al Tab PowerDNA Explorer AO Tab, Output Subtab PowerDNA Explorer AO Tab, Guardian Subtab PowerDNA Explorer DI Tab PowerDNA Explorer DO Tab, PWM Subtab PowerDNA Explorer DO Tab, Output Subtab PowerDNA Explorer Serial Tab, Configuration Subtab PowerDNA Explorer Serial Tab, Send/Receive Subtab PowerDNA Explorer I2C Tab, Configuration Subtab Write Slave FIFO Command Read Command Write Command Setup Address for Temperature Sensor Send Command to Read Temperature Sensor PowerDNA Explorer CT Tab, Quadrature Mode PowerDNA Explorer CT Tab, Bin Counter Mode PowerDNA Explorer CT Tab, Frequency Mode PowerDNA Explorer CT Tab, Frequency Mode PowerDNA Explorer CT Tab, Frequency Mode PowerDNA Explorer TTL Tab, Configuration Subtab | 38 40 41 42 44 46 47 50 51 52 53 54 54 55 60 60       |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-17<br>3-18<br>3-19<br>3-20         | PowerDNA Explorer for DNx-MF-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38 40 41 42 44 46 47 50 51 52 53 54 54 55 60 60       |

| Chapter | 5 Programming with Low-level API96                                      | ŝ |

|---------|-------------------------------------------------------------------------|---|

| Appendi | x A Accessories                                                         | 1 |

| A-1     | Photo of DNA-STP-MF-101 screw terminal board with DNA-CBL-MF-1M cable12 | 1 |

| A-2     | DNA-STP-MF-101 Pinout                                                   | 3 |

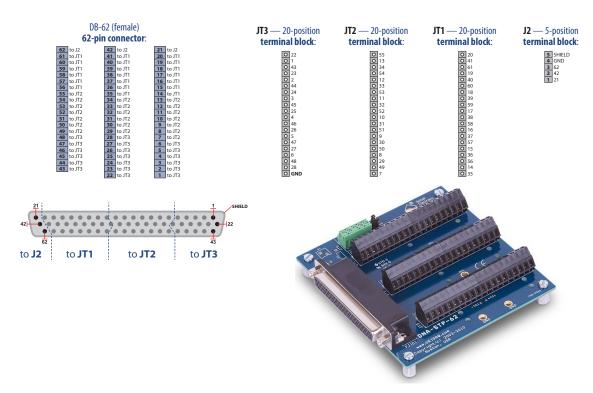

| A-3     | Pinout and Photo of DNA-STP-62 Screw Terminal Panel124                  | 1 |

### **List of Tables**

| Chapter      | 1 Introduction                                        |     |

|--------------|-------------------------------------------------------|-----|

| 1-1          | Analog Input Specifications                           |     |

| 1-2          | Analog Output Specifications                          |     |

| 1-3          | Industrial Digital I/O Specifications                 |     |

| 1-4          | TTL Digital I/O Specifications                        |     |

| 1-5          | Counter/Timer Specifications                          |     |

| 1-6          | RS-232/422/485 Port Specifications                    |     |

| 1-7          | I2C Port Specifications                               |     |

| 1-8          | General and Environmental Specifications              | 11  |

| Chapter      | 2 I/O Functional Descriptions                         | 12  |

| 2-1          | DNx-MF-101 Counter Registers                          |     |

| 2-2          | I2C Bus Conditions                                    | 27  |

| 2-3          | LED Indicators                                        | 29  |

| 2-4          | Analog I/O Pin Descriptions                           | 31  |

| 2-5          | Industrial Digital I/O Pin Descriptions               | 31  |

| 2-6          | Logic-level Digital I/O Pin Descriptions              | 31  |

| Chanter      | 3 PowerDNA Explorer                                   | 37  |

| -            | •                                                     |     |

| -            | 4 Programming with High-level API                     |     |

| 4-1          | DAQ Modes Supported by UeiDaq Framework               |     |

| 4-2          | Analog Input Ranges (Volts)                           |     |

| 4-3<br>4-4   | Diagnostic Channel Numbers                            |     |

| 4-4<br>4-5   | High-level API for Serial Port Configuration          |     |

| 4-5<br>4-6   | High-level API for Slave Port Configuration           |     |

| . •          | · ·                                                   |     |

|              | 5 Programming with Low-level API                      |     |

| 5-1          | DAQ Modes Supported by the Low-level API              |     |

| 5-2          | Low-level Analog I/O API                              |     |

| 5-3          | Low-level Digital I/O API                             |     |

| 5-4          | Low-level Counter API                                 |     |

| 5-5          | Counter Configuration Parameters                      |     |

| 5-6          | Low-level Serial Port API                             |     |

| 5-7          | Serial Port Configuration Parameters                  |     |

| 5-8          | Low-level I2C Port API                                |     |

| 5-9          | I2C Configuration Parameters                          |     |

| 5-10         | Raw Mode Commands                                     |     |

| 5-11         | Low-level Asynchronous Events API                     |     |

| 5-12         | DMap Channels                                         |     |

| 5-13         | VMap Subsystems and Channels for Social Communication |     |

| 5-14<br>5-15 | VMap Subsystems and Channels for Serial Communication |     |

| J-13         | Aviviap Charmers                                      | 118 |

| Append       | ix A Accessories                                      | 121 |

### **Chapter 1** Introduction

This manual outlines the feature set and use of the DNx-MF-101, a multifunction board with analog and digital I/O, an I<sup>2</sup>C port, and a serial port.

The following sections are provided in this chapter:

- Organization of this Manual (Section 1.1)

- Manual Conventions (Section 1.2)

- Naming Conventions (Section 1.3)

- Related Resources (Section 1.4)

- Before You Begin (Section 1.5)

- DNx-MF-101 Features (Section 1.6)

- Technical Specifications (Section 1.7)

## 1.1 Organization of this Manual

This DNx-MF-101 User Manual is organized as follows:

#### Introduction

Chapter 1 summarizes the features and specifications of the DNx-MF-101.

#### • I/O Functional Descriptions

Chapter 2 describes the device architecture, logic, and connectivity of the DNx-MF-101 subsystems.

#### • PowerDNA Explorer

Chapter 3 shows how to explore DNx-MF-101 features through a GUI-based application.

#### Programming with High-level API

Chapter 4 describes how to configure the DNx-MF-101, read data, and write data with the Framework API.

#### Programming with Low-level API

Chapter 5 provides an overview of C commands for configuring and using the DNx-MF-101.

#### Accessories

Appendix A provides a list of accessories available for use with the DNx-MF-101.

# 1.2 Manual Conventions

The following conventions are used throughout this manual:

Tips are designed to highlight quick ways to get the job done or to reveal good ideas you might not discover on your own.

CAUTION! advises you of precautions to take to avoid injury, data loss, and damage to your boards or a system crash.

**NOTE:** Notes alert you to important information.

| Typeface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                              | Example                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------|

| bold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | field or button names                    | Click Scan Network           |

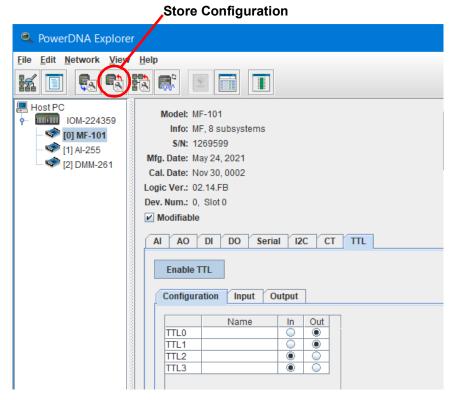

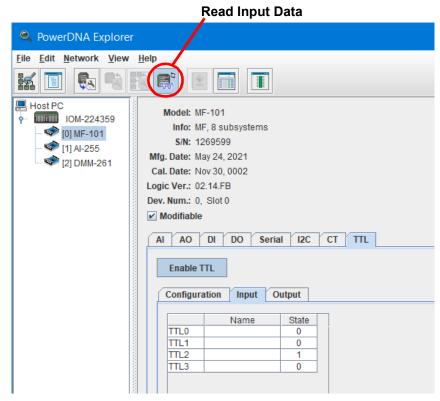

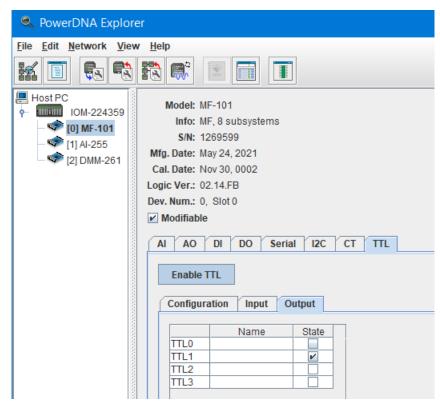

| »                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | hierarchy to get to a specific menu item | File » New                   |