The High-Performance Alternative

# PowerDNx 1PPS / PTP Synchronization Interface Manual

DNx 1PPS / PTP synchronization interface for PPCx & -1G Cube and RACK series systems

#### May 2018

PN Man-DNx-Sync

© Copyright 1998-2018 United Electronic Industries, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form by any means, electronic, mechanical, by photocopying, recording, or otherwise without prior written permission.

Information furnished in this manual is believed to be accurate and reliable. However, no responsibility is assumed for its use, or for any infringement of patents or other rights of third parties that may result from its use.

All product names listed are trademarks or trade names of their respective companies.

See the UEI website for complete terms and conditions of sale: http://www.ueidaq.com/cms/terms-and-conditions/

CE

#### **Contacting United Electronic Industries**

#### Mailing Address:

27 Renmar Avenue Walpole, MA 02081 U.S.A.

For a list of our distributors and partners in the US and around the world, please contact our support team:

#### Support:

| Telephone: | (508) 921-4600 |

|------------|----------------|

| Fax:       | (508) 668-2350 |

Also see the FAQs and online "Live Help" feature on our web site.

#### **Internet Support:**

| Support:  | support@ueidaq.com   |

|-----------|----------------------|

| Website:  | www.ueidaq.com       |

| FTP Site: | ftp://ftp.ueidaq.com |

#### **Product Disclaimer:**

#### WARNING!

# DO NOT USE PRODUCTS SOLD BY UNITED ELECTRONIC INDUSTRIES, INC. AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

Products sold by United Electronic Industries, Inc. are not authorized for use as critical components in life support devices or systems. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Any attempt to purchase any United Electronic Industries, Inc. product for that purpose is null and void and United Electronic Industries Inc. accepts no liability whatsoever in contract, tort, or otherwise whether or not resulting from our or our employees' negligence or failure to detect an improper purchase.

## Specifications in this document are subject to change without notice. Check with UEI for current status.

### **Table of Contents**

| Chapter                                                   | 1 Introduction                                                                                                                                                                                                                                           |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                       | Organization of this Manual 1                                                                                                                                                                                                                            |

| 1.2<br>1.2.1<br>1.2.2<br>1.2.3                            | PPS / PTP Synchronization Overview       3         PTP Synchronization       3         PPS Synchronization       4         Determining Product Versions       5                                                                                          |

| 1.3                                                       | Features 6                                                                                                                                                                                                                                               |

| 1.4<br>1.4.1                                              | External Connections for Synchronization                                                                                                                                                                                                                 |

| 1.5<br>1.5.1<br>1.5.2                                     | Hardware System Configuration Examples       9         Synchronization Using an External 1PPS Signal       9         Synchronization Using IEEE-1588 PTP Standard       12                                                                               |

| 1.6<br>1.6.1<br>1.6.2<br>1.6.3                            | Internal Connections & Resources for Synchronization       15         Internal SYNC Bus       15         Adaptive Digital PLL       17         I/O Board Clock & Trigger Resources       18                                                              |

| 1.7                                                       | I/O Board Clock & Trigger Configuration                                                                                                                                                                                                                  |

| Chapter                                                   | 2 Programming the Synchronization Interface                                                                                                                                                                                                              |

| 2.1                                                       | About the Sync API                                                                                                                                                                                                                                       |

| 2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6 | Sync Structure for Hardware Configuration22Sync Scheme Structure22Section A: IOM SYNC Source Configuration23Section B: Master Server Configuration25Section C: Clock Configuration26Section D: Trigger Configuration28Section E: SyncOut Configuration31 |

| 2.3                                                       | Setting up the Sync Scheme                                                                                                                                                                                                                               |

| 2.4                                                       | Setting up PTP Server Parameters                                                                                                                                                                                                                         |

| 2.5                                                       | Programming I/O Board Clocks                                                                                                                                                                                                                             |

| 2.6<br>2.6.1                                              | Setting I/O Board Triggers    37      Arming Triggers    37                                                                                                                                                                                              |

| 2.7<br>2.7.1                                              | Setting I/O Board Timestamp Reference       38         Setting/Resetting Timestamps       38                                                                                                                                                             |

| 2.8                                                       | Retrieving Status                                                                                                                                                                                                                                        |

| 2.9                                                       | Retrieving PTP Status                                                                                                                                                                                                                                    |

| 2.10                                                      | Retrieving UTC Time                                                                                                                                                                                                                                      |

| 2.11                                                      | Disabling Sync / Releasing Sync Hardware                                                                                                                                                                                                                 |

| Chapter                                                   | 3 System Configuration Tutorials                                                                                                                                                                                                                         |

| 3.1<br>3.1.1                                              | Configuring Synchronization to an External PPS       48         Connecting Hardware for 1PPS Synchronization       48                                                                                                                                    |

| at 2018                                                   | May 2019                                                                                                                                                                                                                                                 |

| 3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                          | Configuring a UEI Chassis as 1PPS Master       49         Configuring a UEI Chassis as 1PPS Slave       53         Configuring Synchronized I/O Board Clocks       57         Configuring Synchronized Triggers & Timestamps       62                                                                  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                   | Configuring Hardware for PTP Synchronization       67         Configuring PTP Interface Parameters       68         Configuring a PTP Grandmaster       69         Configuring a Boundary Clock (IEEE-1588-capable Switch)       72         Configuring a UEI Chassis for PTP Synchronization       76 |

| Chapter                                                   | 4 Code Examples                                                                                                                                                                                                                                                                                        |

| 4.1                                                       | About Sync Code Examples 84                                                                                                                                                                                                                                                                            |

| 4.2                                                       | Supported Data Acquisition Modes for Sync Interface                                                                                                                                                                                                                                                    |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6 | Example Code for Synchronization in RtVMap Mode.85Initialization (RtVMap)86Configuration (RtVMap)89Verify ADPLL Status (RtVMap)90Arm Trigger & Reset Timestamp (RtVMap)91Send / Receive Messages (RtVMap)91Stop Cleanly (RtVMap)92                                                                     |

| 4.4<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>4.4.6 | Example Code for Synchronization in ACB Mode93Initialization (ACB)93Configuration (ACB)97Verify ADPLL Status (ACB)99Reset Timestamp and Arm Trigger (ACB)100Send / Receive Messages (ACB)100Stop Cleanly (ACB)101                                                                                      |

| Append                                                    | lix A                                                                                                                                                                                                                                                                                                  |

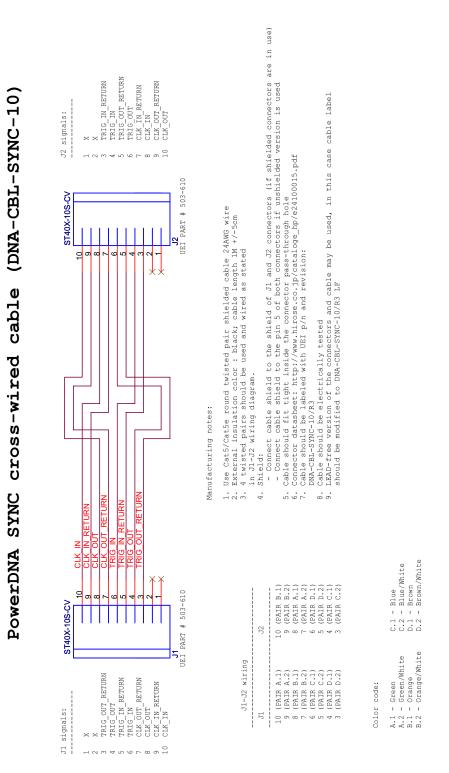

| A.1                                                       | DNA-CBL-SYNC-10/R3 Cable & Schematic                                                                                                                                                                                                                                                                   |

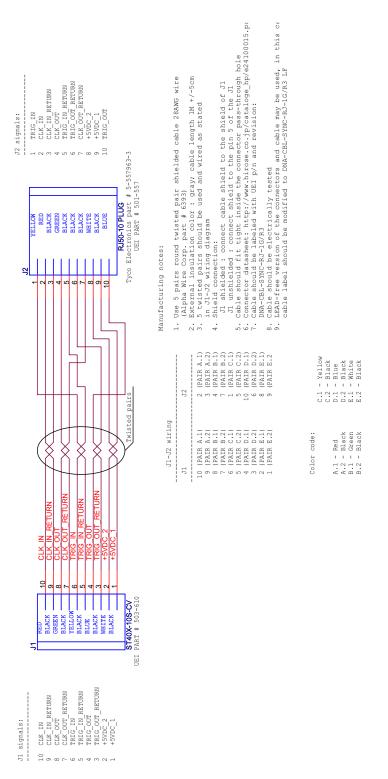

| A.2                                                       | DNA-CBL-SYNC-RJ-1G/R3 Cable Schematic                                                                                                                                                                                                                                                                  |

| A.3                                                       | DNA-STP-SYNC-1G STP Panel                                                                                                                                                                                                                                                                              |

## **List of Figures**

| Chapte | 1 Introduction                                                               |      |

|--------|------------------------------------------------------------------------------|------|

| 1-1    | Connectors on PPCx-1G Cube                                                   |      |

| 1-2    | Pinouts of Sync Connectors on UEI Chassis                                    | 8    |

| 1-3    | Connection Diagram for 2-cube 1PPS Synchronization                           |      |

| 1-4    | Interconnection Diagram for Multi-chassis External 1PPS Synchronization      | .10  |

| 1-5    | Block Diagram of DNA-STP-SYNC-1G                                             |      |

| 1-6    | Example Configuration - PTP Master Clock / Boundary Clock / Slaves           | .12  |

| 1-7    | Example Configuration - UEI Chassis as PTP Master                            |      |

| 1-8    | Example Configuration - Separate Operation and PTP Network                   |      |

| 1-9    | Schematic of Sync Connections on Cube I/O Board                              |      |

| 1-10   | Block Diagram of Example SYNC Bus Connections                                |      |

| 1-11   | Diagram of Connecting to the Sync Interface Bus over Individual I/O Boards   | .20  |

| Chapte | r 2 Programming the Synchronization Interface                                | . 21 |

| Chapte | r 3 System Configuration Tutorials                                           | 47   |

| 3-1 ·  | Example Hardware Configuration for External 1PPS                             | .48  |

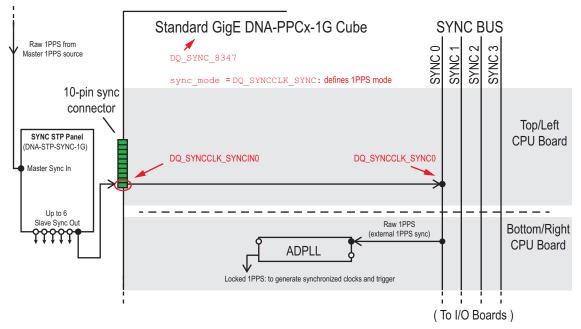

| 3-2    | Block Diagram of Master Configuration                                        | 51   |

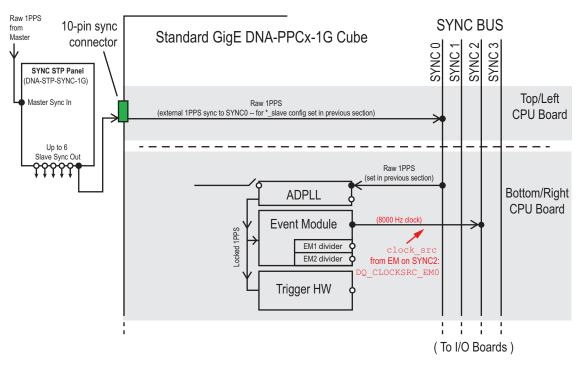

| 3-3    | Block Diagram of Slave Configuration                                         | .55  |

| 3-4    | Block Diagram of Slave Configuration                                         |      |

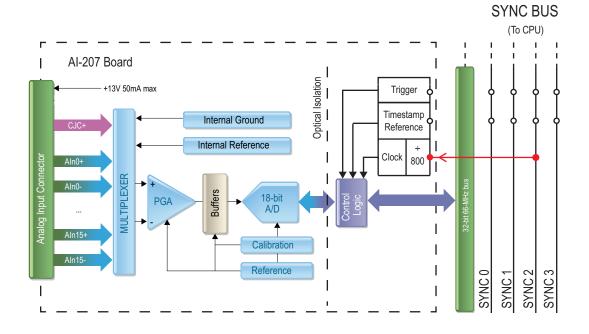

| 3-5    | Diagram of Connecting Clock from SYNC2 to AI-207                             | .61  |

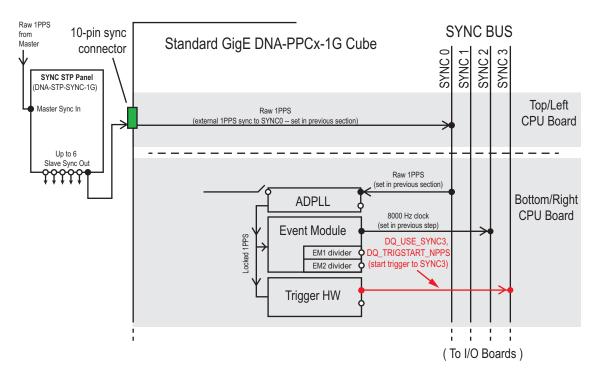

| 3-6    | Block Diagram of Slave Configuration                                         | 63   |

| 3-7    | Diagram of Connecting Trigger & Timestamp Reference from SYNC to AI-207 Boar |      |

| 3-8    | Example of PTP Hardware Configuration                                        |      |

| 3-9    | Rear of the SecureSync <sup>™</sup> PTP Grandmaster                          | .69  |

| 3-10   | Spectracom Grandmaster Dashboard                                             |      |

| 3-11   | Spectracom Grandmaster PTP Config Screen                                     |      |

| 3-12   | Spectracom PTP Grandmaster PTP Advanced Screen                               |      |

| 3-13   | UEI NIC1 Ports                                                               |      |

| 3-14   | Boundary Clock Dashboard                                                     |      |

| 3-15   | Boundary Clock PTP Settings Screen                                           |      |

| 3-16   | Boundary Clock PTP Settings Screen                                           |      |

| 3-17   | Block Diagram of PTP Configuration on UEI CPU Board                          |      |

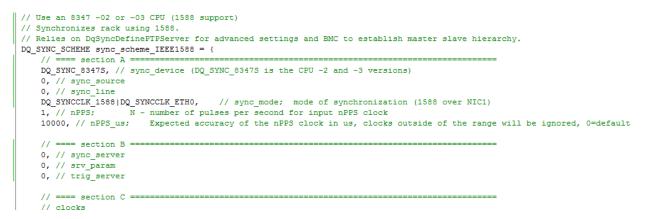

| 3-18   | Code Snippet of Synchronization Structure Settings for PTP Sync              | .78  |

| •      | r 4 Code Examples                                                            |      |

| A-1    | Photo of DNA-CBL-SYNC-10/R3 Cable                                            |      |

| A-2    | Schematic of DNA-CBL-SYNC-10/R3 Cable                                        |      |

| A-3    | Photo of DNA-CBL-SYNC-RJ-1G Cable                                            |      |

| A-4    | Schematic of DNA-CBL-SYNC-10/R3 Cable                                        | 105  |

#### Chapter 1 Introduction

This manual provides documentation for synchronizing UEI Cube and RACK systems.

**1PPS synchronization** is supported on UEI systems that have CPU Logic 02.12.2D (2017) or later. (See Section 1.2.3 for checking logic versions.)

IEEE-1588 synchronization is supported on -02 and -03 versions of UEI Cube and RACK chassis with CPU Logic 02.12.46 (2018) or later.

NOTE: The software and API described in Chapters 2, 3, and 4 of this manual are for programming with the low-level C libraries; For users programming with the DAQLIB framework (C++, C#, LabVIEW, etc.), please refer to the UeiDag Framework User Manual.

Chapter 1 contains the following sections:

- Organization of this Manual (Section 1.1)

- PPS / PTP Synchronization Overview (Section 1.2)

- Features (Section 1.3)

- External Connections for Synchronization (Section 1.4)

- Sync Connector Pinouts (Section 1.4.1)

- Hardware System Configuration Examples (Section 1.5)

- Internal Connections & Resources for Synchronization (Section 1.6)

- I/O Board Clock & Trigger Configuration (Section 1.7)

- 1.1 Organization This 1PPS / PTP Sync Interface User Manual is organized as follows: of this Manual

- Introduction

Chapter 1 provides an overview of the synchronization interface features for various chassis and board models, device architecture, connectivity and logic.

- **Programming the SYNC Interface** Chapter 2 provides an overview of the low-level API functions that configure the synchronization interfaces for UEI cube and rack systems.

- **Tutorials** •

Chapter 3 provides step by step tutorials for setting up hardware and software for synchronization to an external 1PPS reference and synchronization using the IEEE-1588 / PTP standard.

- **Example Code** • Chapter 4 provides example code for setting up synchronization in different data acquisition modes.

- **Appendix A Accessories** This appendix provides descriptions of cable accessories and the SYNC STP board available for 1PPS / PTP Sync Interface.

- Index

This is an alphabetical listing of the topics covered in this manual.

A glossary of terms used with the PowerDNA Cube/RACK and I/O boards can be viewed or downloaded from www.ueidag.com.

#### Manual Conventions

To help you get the most out of this manual and our products, please note that we use the following conventions:

Tips are designed to highlight quick ways to get the job done or to reveal good ideas you might not discover on your own.

NOTE: Notes alert you to important information.

**CAUTION!** Caution advises you of precautions to take to avoid injury, data loss, and damage to your boards or a system crash.

Text formatted in **bold** typeface generally represents text that should be entered verbatim. For instance, it can represent a command, as in the following example: "You can instruct users how to run setup using a command such as **setup.exe**."

**Bold** typeface will also represent field or button names, as in "Click **Scan Network**."

Text formatted in fixed typeface generally represents source code or other text that should be entered verbatim into the source code, initialization, or other file.

#### **Examples of Manual Conventions**

Before plugging any I/O connector into the Cube or RACKtangle, be sure to remove power from all field wiring. Failure to do so may cause severe damage to the equipment.

#### Usage of Terms

Throughout this manual, the term "Cube" refers to either a PowerDNA Cube product or to a DNR- RACKtangle<sup>™</sup> rack mounted system, whichever is applicable. The term DNR- is a specific reference to the RACKtangle, DNA- to the PowerDNA I/O Cube, and DNx to refer to both.

- **1.2 PPS / PTP** The UEI synchronization interface provides hardware and software resources to synchronize one or more chassis (Cubes or RACKs) to an external resource.

**nization** Systems can synchronize multiple, distributed chassis using either of the following:

- IEEE-1588 Precision Time Protocol (PTP) over IPv4/UDP Ethernet

- External pulse-per-second (PPS) reference signal via the 10-pin sync ports

- **1.2.1PTP Synchro-**<br/>nizationPTP synchronization is supported on -02 and -03 versions of UEI Cubes and<br/>RACKs having CPU Logic 02.12.46 (2018) or later.

The IEEE-1588 PTP standard defines the protocol for establishing a master/ slave relationship between a reference clock source (the PTP grandmaster) and all other devices in the system that will synchronize their clocks to the master clock (slaves).

The master/slave hierarchy is established through an exchange of PTP packets containing clock attributes (clock accuracy, etc.). PTP devices on the network process the clock attributes announced by a potential master using an algorithm of prioritized attributes called the Best Master Clock Algorithm (BMCA). If a grandmaster-capable device determines it has better clock attributes than those already announced, it announces, and this continues until the grandmaster for the system is determined.

The grandmaster is responsible for sending PTP Sync packets containing traffic timestamping data. Slave devices receive the PTP packets, determine network latency, and derive a local synchronized reference signal from timestamp data.

# **1.2.1.1 PTP** UEI's implementation of the IEEE-1588 standard supports the following: **Specification**

- PTP v2 (IEEE 1588-2008) supported on -02 and -03 versions of UEI GigE Cubes and RACKS (products with Freescale 8347/8347E CPUtypes only)

- PTP over IPv4/UDP (Annex D)

- TBD resolution (packet timestamping)

- TBD accuracy (master to slave)

- Multicast transmission mode (unicast point-to-point is not currently supported)

- Hardware timestamping

- Grandmaster capability:

- Hosted deployments of UEI systems are capable of being a PTP grandmaster or slave device

- Standalone deployments (UEIPACs) can only be slave devices

- Clock Class: clockClass attribute is 248 (default clock class)

- Capable of connecting via an end-to-end boundary clock (transparent clocks not currently supported)

- Supported for I/O board synchronization only

Note that the chassis real-time clock cannot be synchronized to PTP time.

#### **1.2.2 PPS Synchronization** Synchronization to an external pulse per second (PPS) reference is supported on UEI Cubes and RACKs having CPU Logic 02.12.2D (2017) or later.

UEI chassis can synchronize to an external pulse per second reference signal provided by a master source. Typically this is a one pulse per second (1PPS) signal. The 1PPS is routed to each chassis and input over the 10-pin sync port at the front of the Cube or RACK chassis.

A UEI chassis can also act as a master 1PPS source and generate and route its 1PPS reference signal for distribution to all slave chassis in the system

Once cubes and/or RACKs lock to the common 1PPS pulse, they can be programmed to generate internal clocks and triggers for all configured I/O boards in a system, allowing time alignment among each of the I/O boards on all of the synchronized chassis, as well as allowing the synchronization of timestamps.

#### 1.2.2.1 PPS 1PPS Input/Output: Specification • pulse\_per\_set

- pulse-per-second (configurable)

- TTL signal levels

- TBD accuracy

**NOTE:** All Cubes and RACKs synchronizing to the same 1PPS pulse will lock with approximately a 100 ns accuracy range to each other.

#### Inter-connect Delays

Connection delays associated with PPS routing through cabling and screw terminal panels (STPs) are provided in Section 1.5.1.3 on page 11.

| 1.2.3                                                          | Determining<br>Product<br>Versions | You can check the logic version installed on the CPU of your chassis to verify<br>which synchronization methods your system supports.<br>You can use PowerDNA Explorer, a GUI application for communicating with a<br>Cube or RACK chassis, or you can use the serial port.<br>Getting a hardware report using PowerDNA Explorer is the preferred method.                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2.3.1 Checking CPU<br>Logic using<br>PowerDNA<br>Explorer    |                                    | <ul> <li>To determine the logic version using PowerDNA Explorer, do the following:</li> <li>1. Open PowerDNA Explorer:<br/>On Windows systems, you can access PowerDNA Explorer from the<br/>Windows Start menu:<br/>Start &gt; All Programs &gt; UEI &gt; PowerDNA &gt; PowerDNA Explorer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                |                                    | On Linux systems, you can access PowerDNA Explorer under the UEI installation directory ( <powerdna-x.y.z>/explorer) and type: java -jar PowerDNAExplorer.jar</powerdna-x.y.z>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                |                                    | <ol> <li>In the Menu bar of PowerDNA Explorer, click<br/>View &gt; Show Hardware Report.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                |                                    | 3. Note the Logic version under the Layer: CPU section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.2.3.2 Checking CPU To<br>Logic using<br>Serial<br>Connection |                                    | <ol> <li>To determine the logic version using a serial connection, do the following:         <ol> <li>Install a serial cable between your host PC and the UEI chassis.</li> </ol> </li> <li>Open a serial communication application, (e.g., PuTTY, MTTTY, minicom) on your host PC, and configure settings to 57600 bits/s, 8 data bits, 1 stop bit and no parity, and then connect.</li> <li>Once connected, type devtbl logic <return> at the command prompt. The CPU board is designated as DevN "14", and the logic version is listed under the Logic column.</return></li> <li>To check the CPU version, type devtbl <return>. The CPU board is listed as "cpu" under the Phy/Virt column, and the version number is</return></li> </ol> |

|                                                                |                                    | NOTE: For a UEIPAC-based chassis, you can also access the command<br>prompt using telnet or ssh by connecting to the chassis CPU over the<br>Ethernet port. Once connected, use the commands listed in<br>steps 3 and 4 to check versioning.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **1.3 Features** The following is an overview of the synchronization interface features.

- Synchronization mode options:

- 1PPS synchronization

- IEEE 1588 PTP synchronization

- Support for using DNx-IRIG-650 board as a source for 1PPS & GPS synchronization

- NTP synchronization in later versions of the hardware

- Synchronization signal routing:

- Systems synchronizing to an external 1PPS signal receive and transmit the 1PPS signal via a 10-pin sync connector at the front of the chassis

- Systems synchronizing using the IEEE-1588 PTP standard can receive packets via the NIC1 or NIC2 Ethernet port

- Master / Slave configuration:

- Chassis can be configured as PPS master (generate and route the 1PPS) or slave (receive an external 1PPS)

- Hosted deployments synchronizing to the IEEE PTP standard can be a PTP slave or grandmaster

- Standalone deployments (UEIPACs) synchronizing to the IEEE PTP standard can only be a PTP slave

- Clock options:

- Clocks can be synchronized to the external reference and distributed to I/O boards

- If an application requires it, I/O boards can be run from other clock sources that are not synchronized to the IEEE PTP standard or to an external 1PPS reference

- Trigger options:

- · Synchronization requires all boards to start together

- The start trigger can be an external hardware trigger, a software trigger, or generated relative to a PPS edge

- The stop trigger can be programmed to stop after a time or number of scans

#### 1.4 External Connections for Synchronization

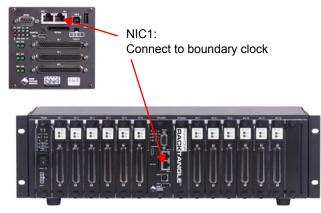

**For PTP synchronization,** PTP hardware timestamping is supported on either Ethernet port. Using NIC1 (Ethernet port 0) or NIC2 (Ethernet port 1) is user-configurable.

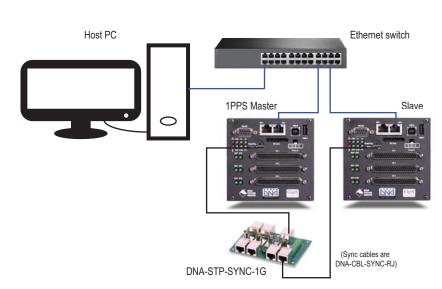

**For synchronization to an external 1PPS signal**, the 1PPS routes into or out of a UEI chassis through a 10-pin sync connector at the front of the chassis. Note that for systems synchronizing more than 2 chassis to an external 1PPS signal, UEI offers a screw terminal panel (STP), the DNA-STP-SYNC-1G.

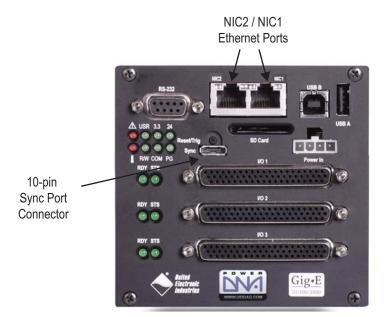

Refer to **Figure 1-1** for locations of the sync port and Ethernet ports.

Figure 1-1 Connectors on PPCx-1G Cube

On a PowerDNA PPCx Cube (5200 CPU: i.e., DNA-PPC5/8/9 or UEIPAC-300/600), the 10-pin sync connector provides one sync input (Sync In 0) and one sync output (Sync Out 0) for routing an external 1PPS signal. PTP synchronization is not supported on these product versions.

On a PowerDNA PPCx-1G Cube and DNR/F RACK chassis (8347 CPUs), the 10-pin sync connector provides two sync inputs and two sync outputs. Users have a choice of which sync pin on the connector to route an external 1PPS signal. This is configurable in software. (For PTP synchronization, the sync port is not used and all synchronization occurs over the Ethernet ports).

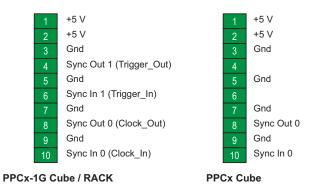

**1.4.1** Sync

Pinouts of the sync connector for the PPCx-1G Cube / RACK

**Connector** and the PPCx Cube (i.e., DNA-PPC5/8/9 or UEIPAC-300/600) are shown below in Figure 1-2.

Figure 1-2 Pinouts of Sync Connectors on UEI Chassis

**NOTE:** For information regarding wiring delays associated with cat5e or better cables and screw terminal panels (STPs) for synchronization, please see "Connection Delays when Using Multiple Chassis" on page 11.

- **1.5**Hardware<br/>System<br/>Configuration<br/>ExamplesThe following sections provide examples of connecting hardware for<br/>synchronizing with an external 1PPS source or using PTP.**Configuration**<br/>ExamplesExample tutorials of configuring UEI chassis and other components to support<br/>these configurations are provided in Chapter 3.

- 1.5.1 Synchronization Using an External

1PPS Signal

To synchronize a multi-chassis system, one cube (or RACK) can be designated as the 1PPS master and the others as slaves. Alternatively, all UEI chassis can be configured as slaves to non-UEI 1PPS-generating hardware.

- **1.5.1.1** Example of Syncing to an External 1PPS in a 2-Chassis System

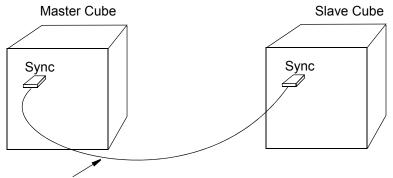

An example of synchronizing a 2-chassis system using one chassis as the 1PPS master and the second as its slave is shown in Figure 1-3.

DNA-CBL-SYNC-10/R3 (8-conductor, 30-inch, cross-connected, Sync connectors on both ends)

#### Figure 1-3 Connection Diagram for 2-cube 1PPS Synchronization

For more information about UEI synchronization cables, refer to Appendix A.

**NOTE:** The absolute maximum signal frequency supported over the sync connector is 5 MHz.

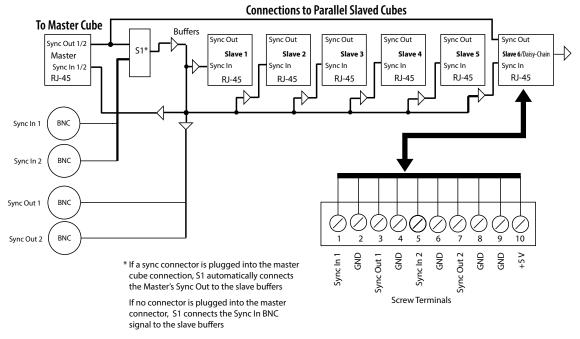

**1.5.1.2Example of**<br/>Syncing to an<br/>External 1PPS<br/>in a Multi-<br/>chassis<br/>SystemFor synchronizing multiple chassis to an external 1PPS master, UEI offers a<br/>screw terminal panel (STP) that can serve up to 6 slave ports on the STP.As an example configuration, Figure 1-4 shows a UEI chassis acting as the<br/>1PPS master; however, note that any 1PPS source could be used.<br/>Additional slaves can be added to the system by daisy-chaining STP boards<br/>together. Refer to the UEI DNA-STP-SYNC-1G Synchronization Interconnection

Panel documentation for more information.

**NOTE:** Connection delays through cabling and STP are described in Section 1.5.1.3 on page 11.

Figure 1-4 Interconnection Diagram for Multi-chassis External 1PPS Synchronization

**Figure 1-5** provides a block diagram of the DNA-STP-SYNC-1G panel. For more information about UEI synchronization cables, refer to Appendix A.

Figure 1-5 Block Diagram of DNA-STP-SYNC-1G

- 1.5.1.3 Connection Delays when Using Multiple Chassis

Delay through 1/2 foot of cat5e cable is approximately 1 ns

Delay through DNA-STP-SYNC-1G (Figure 1-5) is approximately 100 ns

- **NOTE:** Cable and STP panel delays were tested at UEI using up to 800 foot cables (1.6  $\mu$ s).

#### 1.5.2 Synchronization Using IEEE-1588 PTP Standard

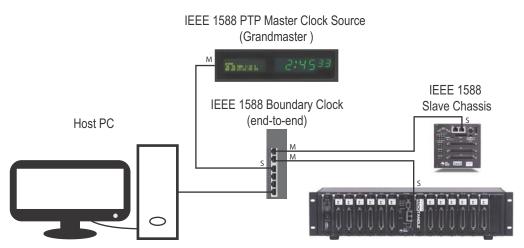

For optimal synchronization among UEI slave chassis, the Grandmaster clock and IEEE-1588 capable Ethernet switch (configured as an end-to-end boundary clock) must support hardware timestamping.

ndard Examples in this section use the following network hardware for synchronizing a system using the IEEE-1588 PTP standard:

| UEI slave chassis                                  | -02 and -03 versions of UEI's GigE RACKtangle and Cube                                                                                                                                                   |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE 1588 PTP grandmaster<br>(master clock source) | Example PTP masters include:<br>Spectracom's SecureSync™ PTP grandmaster<br>or -02 and -03 versions of UEI's GigE RACKtangle and Cube                                                                    |

| IEEE 1588-capable<br>Industrial switch             | Examples include managed Ethernet switches with PTP support<br>Note that UEI's current IEEE-1588 implementation requires<br>configuring your IEEE 1588-capable switch as an end-to-end<br>boundary clock |

| Host PC                                            | Used to configure a PTP grandmaster and boundary clock and to run the user application in PowerDNA (hosted) deployments (non UEIPAC deployments)                                                         |

A **boundary clock** is an Ethernet switch that additionally manages IEEE-1588 packets. It redistributes PTP packets from the grandmaster to an isolated subnet of slaves. A boundary clock acts as a slave to the grandmaster and then becomes the master clock to any slave devices on the subnet. All clocks ultimately derive their time from the grandmaster clock.

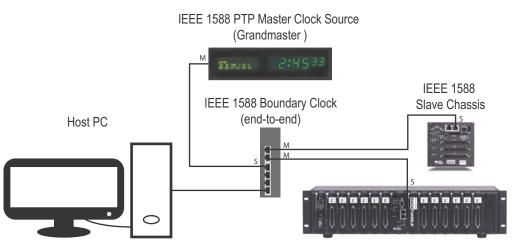

1.5.2.1 Example Configuration Using Same NIC for Ethernet and PTP Packets Figure 1-6 shows the following example configuration:

- UEI Cubes & RACKs using PTP synchronization in hosted deployment

- Host PC running user application

- IEEE 1588 PTP master clock source providing synchronization packets

- (1) IEEE 1588 boundary clock routing PTP packets between the PTP master and UEI slave chassis (NIC1) and application & data packets between host PC & UEI chassis (NIC1)

Figure 1-6 Example Configuration - PTP Master Clock / Boundary Clock / Slaves

- 1.5.2.2

Example

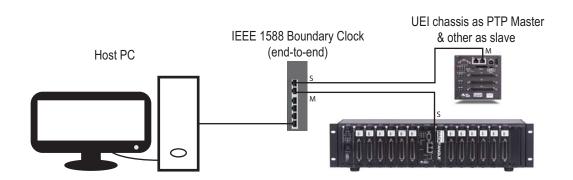

A UEI Cube or RACK is capable of serving as the PTP master of your system.

Configuration

Figure 1-7 shows the following configuration:

Using UEI

UEI Cube of RACK is capable of serving as the PTP master of your system.

- UEI Cubes & RACKs using PTP synchronization in hosted deployment

- Chassis as PTP Master

- Host PC running user application

- UEI Cube acting as 1588 PTP master clock source providing synchronization packets

- (1) IEEE 1588 boundary clock routing PTP packets and application & data packets between UEI chassis (NIC1) & host PC

#### Figure 1-7 Example Configuration - UEI Chassis as PTP Master

Which Cube or RACK is PTP master is determined by the best master clock algorithm, (BMCA). UEI also supports a debug mode, where the selection of the PTP master can be forced using a setting in the configuration structure.

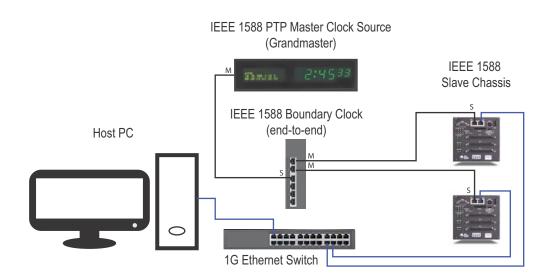

- 1.5.2.3 Example Configuration Using Separate NICs for Operation and PTP

As an alternative, you can configure two separate networks: one for operation and one for PTP synchronization.

Figure 1-8 shows the this configuration:

UEI Cubes & RACKs using PTP synchronization in hosted deployment

Host PC running user application

- IEEE 1588 PTP Grandmaster clock source providing synchronization

- (1) IFEE 1588 boundary clock routing PTP nackets between

- (1) IEEE 1588 boundary clock routing PTP packets between PTP master and UEI slave chassis (NIC2)

- (1) 1G network switch routing application & data packets between host PC & UEI chassis (NIC1)

Figure 1-8 Example Configuration - Separate Operation and PTP Network

Packets

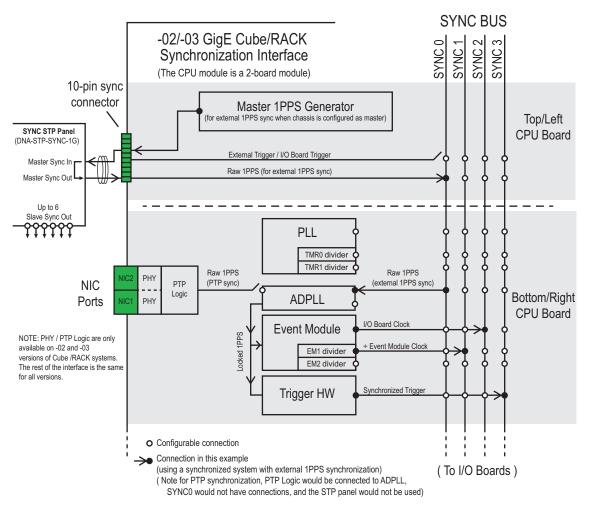

# 1.6 Internal Connections & Resources for Synchro-

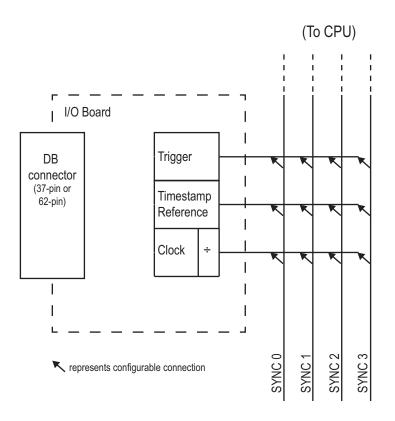

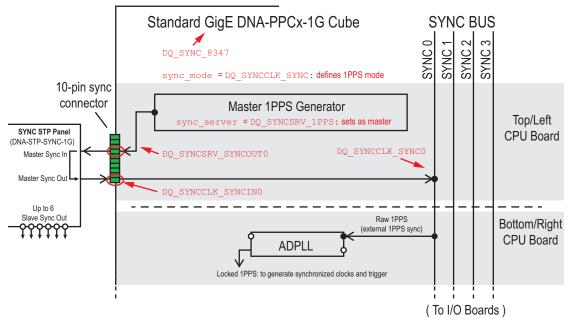

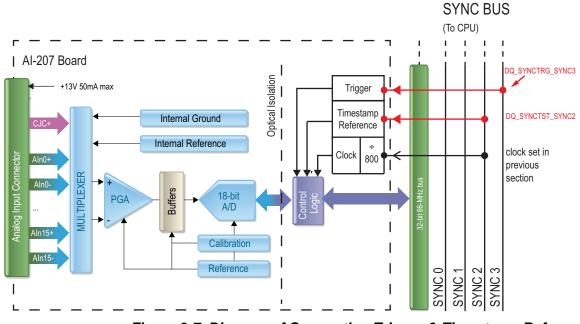

UEI chassis use an internal interboard bus that routes synchronization signals between the CPU board and I/O boards via four internal SYNC lines. SYNC lines are designated SYNC0 through SYNC3. The schematic below shows how the SYNC lines route through the main connector of a DNA Cube I/O board.

- On a Cube chassis, interboard signals are bused through stacked connectors. **Figure 1-9** shows SYNC lines routed to connector labeled JMAIN1.

- On a RACK chassis, interboard bus signals route across the chassis backplane and connect through backplane connectors to each board installed in the RACK.

| B_SYNC2<br>B_SYNC0       | R72                            |              |          | JMAIN1   |          |             |  |

|--------------------------|--------------------------------|--------------|----------|----------|----------|-------------|--|

| B_SYNC1                  | R74                            | DNA_SYNC1    | 1        | 4        | 61       | DNA_SYNC0   |  |

| B_SYNC3                  | R77                            | DNA_SYNC3    | 2        | 2-099061 | 62       | DNA_SYNC2   |  |

| ∞ <b>60</b> <del>-</del> | 22.1                           | GND          | 3        | 3 000063 | 63 ×     |             |  |

| R887                     | са <u>в ка</u> со ст           | B A1         | 4<br>5   | 4        | 64<br>65 | GND         |  |

|                          | <u>.</u>                       | B A5         | 6        | 5 000065 | 66       | B A0        |  |

| >>>>                     | 10K                            | B_A4         | 7        | 6 66     | 67       | B_A2        |  |

|                          |                                | B_A7         | 8        | 8 09 00% | 68       | B_A3        |  |

|                          |                                | B_A11        | 9        | 9 00069  | 69       | B_A6        |  |

| +3.3V 0                  | 2 2 2 2 2 2 2 4 2 <del>4</del> | B_A10<br>GND | 10       | 10 70    | 70       | B_A8<br>GND |  |

|                          | 9 8 8 8 8 8 8 <del>6</del>     | B A15        | 11<br>12 | 11000071 | 71<br>72 | B A9        |  |

|                          |                                | B A14        | 13       | 1272     | 73       | B A12       |  |

#### Figure 1-9 Schematic of Sync Connections on Cube I/O Board

As shown above, each SYNC line is pulled up with a 10 k $\Omega$  resistor to prevent synchronization lines from bouncing and also ensure that proper drive is available from every board. In the PPC8 Cube, for example, the total resistance is 1430  $\Omega$  with a termination current of 2.3 mA.

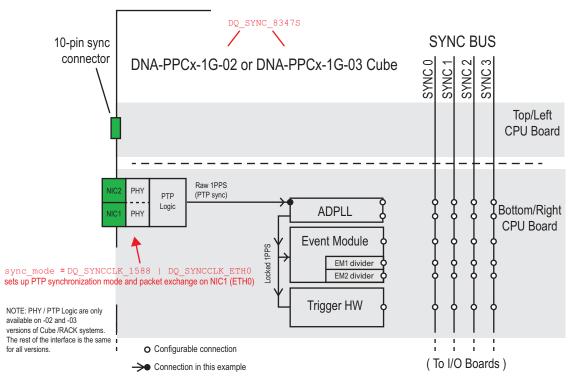

**1.6.1 Internal SYNC Bus** The SYNC lines can be accessed from the chassis CPU board and are accessible to each I/O board in the chassis. The driving source for each of the four SYNC lines is user programmable.

The following are sync sources that can be routed to or from the CPU board over the sync bus:

- External sources routed through the 10-pin sync connector

- A phase-locked loop (PLL) clock generator local to the CPU board

- An adaptive digital phase-locked loop (ADPLL) that validates and follows an external, raw 1PPS or PTP-derived 1PPS reference

- An Event Module that synthesizes and/or divides a CPU generated clock based on the locked 1PPS reference from the ADPLL

- Trigger circuitry

SYNC lines are assigned to hardware resources as defined by configuration settings in a global DQ\_SYNC\_SCHEME structure. See **Chapter 2** for more information about programming the sync interface.

#### Hardware Checks

UEI firmware checks that SYNC line routing is only set once. For example, if the user programs a clock on SYNC line 1 and later programs a trigger on SYNC line 1, the firmware will produce a warning and only connect the last assignment to prevent hardware damage.

# **1.6.1.1** Internal SYNC Each I/O board in a chassis can be programmed to use a clock or trigger resource from the CPU board routed via any of the SYNC lines. Determining which resource is connected to which internal sync line is user configurable.

UEI's synchronization hardware and software allow for highly flexible and customizable system designs. For standardization, we use the following sync line mapping, which you will find in most of our example code:

- SYNC0: raw 1PPS pulse routed to ADPLL for internal use

- SYNC1: Clock source (CPU-generated clock or divided clock that is routed to I/O boards)

- SYNC2: Clock source (usually the Event Module clock locked to the 1PPS pulse and routed to I/O boards)

- SYNC3: CPU generated trigger synchronized to the 1PPS pulse and routed to I/O boards

- **NOTE:** When synchronizing to an external 1PPS reference, one SYNC line is needed to route the raw 1PPS reference to the adaptive digital phase-locked loop (ADPLL) on the CPU board. The other three SYNC lines can be connected to clock and trigger resources as your application requires. Refer to **Figure 1-10**.

#### 1.6.2 Adaptive Digital PLL

The adaptive digital phased-lock-loop (ADPLL) synchronizes to a raw PPS reference signal:

- When synchronizing to an external 1PPS input, a raw 1PPS signal is delivered to the ADPLL via the 10-pin sync connector

- When synchronizing using the PTP standard, a raw 1PPS signal is derived from the PTP timestamps.

The ADPLL produces an internal reference from the raw 1PPS for generating clocks, triggers, and timestamps for all I/O boards installed in the chassis.

The ADPLL is responsible for the following functions:

- validates the raw 1PPS by comparing the incoming signal to a user defined tolerance value

- follows an external/raw 1PPS reference signal and once synchronized continues to produce a 1PPS pulse for internal use in absence of a valid 1PPS raw signal

- provides minimum, maximum, and averaged period values to the software, along with other status data that can be read via an API function call for system monitoring and troubleshooting.

Refer to Section 2.8 on page 39 for more information about API for retrieving status when programming with the low-level C libraries. API for retrieving status when programming with the DAQLIB framework (C++, C#, LabVIEW, etc.) are found in the *UeiDaq Framework User Manual*.

# 1.6.3I/O Board<br/>Clock &<br/>Trigger<br/>ResourcesUsers can program which clock or trigger source each I/O board installed in a<br/>cube or RACK will use.Trigger<br/>ResourcesTo synchronize I/O board clocks in a multi-chassis system, use the Event<br/>Module and/or the Event Module dividers as the clock source for your I/O boards<br/>that you want synchronized. The Event Module is synchronized to the PPS/PTP<br/>reference source.

- Internal Clock Sources are described below in Table 1-1.

- Trigger sources are described on page 19.

Refer to **Chapter 2** for more information about how to program these options.

**1.6.3.1 Clock Sources Table 1-1** provides descriptions of available clock sources:

| Clock Source                                                     | Description                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Event Module<br>(1PPS/PTP synchronized)                          | The Event Module is located on the CPU board and is used to provide<br>synchronized clock sources to I/O boards at user-programmed<br>frequencies.<br>The Event Module requires CPU board logic greater than 12.2D (refer<br>to Section 1.2.3 to learn how to determine CPU board logic).                                         |

|                                                                  | The Event Module receives the locked 1PPS reference from the ADPLL and performs additional stabilization by tracking the number of clocks per PPS and adjusting the frequency to stay within ±1 pulse/clock cycle. This produces a highly-stablized, synchronized clock for use by I/O boards at the rate programmed by the user. |

|                                                                  | Synchronized clock rates are generated to the accuracy of 1 Hz to the programmed rate. The maximum clock rate supported is 1 MHz.                                                                                                                                                                                                 |

|                                                                  | <b>Note</b> : Each I/O board can further divide the clock routed via the SYNC line. EM0 should be programmed with a rate divisible by the clock rates required by each of the I/O boards.                                                                                                                                         |

| Event Module Dividers:<br>EM1 and EM2<br>(1PPS/PTP synchronized) | The main clock produced by the Event Module (EM0) can be routed<br>to either of two 8-bit Event Module clock dividers, EM1 or EM2. Using<br>EM1 or EM2, you can divide the EM0 clock by a maximum of 255.                                                                                                                         |

|                                                                  | This means that three different clocks can be generated by the Event Module: EM0, EM1, and/or EM2.                                                                                                                                                                                                                                |

|                                                                  | To use the divider clocks, the Event Module is programmed and routed to a SYNC line, and then either or both EMx dividers can be programmed and their divided clocks routed to additional SYNC lines.                                                                                                                             |

| PLL                                                              | A phase-locked loop (PLL) onboard the CPU board can be routed<br>throughout the chassis and used as an alternate clock source.<br>The PLL is not synchronized to the PTP/1PPS reference.                                                                                                                                          |

Table 1-1 Clock Sources for PowerDNx Boards

| Clock Source                   | Description                                                                                                                                                                                                                                                                     |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PLL Dividers:<br>TMR0 and TMR1 | The PLL can be divided down by either of two 32-bit timers (TMR0 and TMR1) and routed to SYNC lines for use by I/O boards.                                                                                                                                                      |  |

|                                | To use the dividers, the PLL is programmed and routed to a SYNC line, and either or both dividers can also be programmed and routed. Clocks generated by dividing the PLL are not synchronized to the PTP/1PPS reference.                                                       |  |

| External Clocks                | A clock generated external to the chassis can be routed in through<br>the 10-pin sync connector and made accessible to chassis I/O boards<br>via one of the SYNC lines. An externally generated clock will not be<br>locked to the internal ADPLL or to the PTP/1PPS reference. |  |

| None of the above              | By default, the clock source for I/O boards is generated on the board, divided down from the 66 MHz system clock. Additionally, several boards provide their own onboard PLL: the AI-211, AI-217, AI-218, and AI-228 boards all have this capability.                           |  |

|                                | Neither of these options will be synchronized to the PTP/1PPS reference.                                                                                                                                                                                                        |  |

Table 1-1 Clock Sources for PowerDNx Boards (Continued)

# **1.6.3.2** Trigger UEI systems can trigger from the ADPLL 1PPS signal, an external signal, or software. The start trigger aligns all boards and starts acquisition. For triggers referenced to the ADPLL 1PPS, the stop trigger can be programmed using a user-defined

to the ADPLL 1PPS, the stop trigger can be programmed using a user-defined number of clock cycles of a user-specified clock reference routed to a SYNC line or a user-defined time in milliseconds.

1.7 I/O Board Clock & Trigger Trigger

## Configuration

#### Figure 1-11 Diagram of Connecting to the Sync Interface Bus over Individual I/O Boards

Refer to Section 2.3 on page 33 for API to setup I/O board synchronization options and Section 3.1.4 and 3.1.5 starting on page 57 for a tutorials.

Additionally, IRIG-650 boards can provide a variety of clock and trigger options, which can get routed to the SYNC bus. Please refer to the DNx IRIG-650 data sheet and user's manual for information, and the *PowerDNA API Reference Manual* for API descriptions.

# Chapter 2 Programming the Synchronization Interface

This chapter outlines API and software structures for programming 1PPS / PTP synchronization when programming with the low-level C libraries.

**NOTE:** Refer to the *UeiDaq Framework User Manual* for information about synchronizing systems using the DAQLIB framework (C++, C#, LabVIEW, etc.).

The following sections are included in this chapter:

- About the Sync API (Section 2.1)

- Sync Structure for Hardware Configuration (Section 2.2)

- Setting up the Sync Scheme (Section 2.3)

- Setting up PTP Server Parameters (Section 2.4)

- Programming I/O Board Clocks (Section 2.5)

- Setting I/O Board Triggers (Section 2.6)

- Setting I/O Board Timestamp Reference (Section 2.7)

- Retrieving Status (Section 2.8)

- Retrieving PTP Status (Section 2.9)

- Retrieving UTC Time (Section 2.10)

- Disabling Sync / Releasing Sync Hardware (Section 2.11)

1PPS synchronization is supported after CPU Logic 02.12.2D (2017). PTP synchronization is supported in -02 and -03 versions of the GigE Cube and RACK chassis only.

Refer to Section 1.2.3 for instructions on how to check logic versions.

#### 2.1 About the Sync API

The first step in configuring your UEI system for synchronization is to define your system and hardware configuration.

Configure the following for each UEI chassis requiring synchronization:

- For PTP synchronization, you first configure PTP server parameters using the DqSyncDefinePTP() API.

- Hardware configuration for CPU board and chassis is defined in a software structure of type DQ\_SYNC\_SCHEME, which is set in hardware using the DqSyncDefineSyncScheme() API.

- After that, I/O board clocks, triggers, timestamps and other synchronization options can be set up.

- **NOTE:** The PowerDNAAPI Reference Manual provides detailed descriptions of the DQ\_SYNC\_SCHEME structure and synchronization API, and **Chapter 3** provides tutorials.

DNx 1PPS / PTP Synchronization Interface Chapter 2 22 Programming the Synchronization Interface

- 2.2

Sync

Define signal routing and other synchronization options for each chassis in your system using the sync structure (DQ\_SYNC\_SCHEME).

Hardware

The full structure is shown below. Element options are described in detail in the following sections, Section 2.2.2 thru Section 2.2.6.

- 2.2.1 Sync Scheme The Sync Scheme structure is set up in hardware using the DqSyncDefineSyncScheme() API.

```

typedef struct {

// IOM Sync Source Configuration

// IOM CPU type (5200,8347,or 8347 with PTP capability)

uint32 sync_device;

// where to get nPPS clock to synchronize system

uint32 sync_source;

uint32 sync line;

// which SYNC line to route external 1PPS clock

uint32 sync_mode;

// mode of synchronization

uint32 nPPS;

// N - number of pulses per second for input nPPS clock

// Expected accuracy of the nPPS clock in µs, clocks

uint32 nPPS_us;

outside of the range will be ignored, 0=default

11

// synchronization output: tell IOM to become 1PPS master

uint32 sync_server; // Identify chassis as 1PPS master

uint32 srv_param;

// which external sync connector pin routes 1PPS out

// to the 1PPS slave chassis in the system

// <Reserved>

uint32 trig_server;

// Clock configuration: select clock source for each SYNC line (0 thru 3)

uint32 clock_src[DQL_SYNC_LINES]; // clock source for each SYNC line

// PLL and external clock can be

uint32 clock_tmr[DQL_SYNC_LINES];

// divided on TMR0 or TMR1

uint32 clock_frq[DQL_SYNC_LINES]; // clock frequency (for PLL/EM)

uint32 clock div[DOL_SYNC_LINES]; // clock divider for EMx

uint32 clock_div[DQL_SYNC_LINES];

// clock divider for EMx

// (0 == divide by 1, 2, 3 etc.)

// Trigger Configuration: tell IOM where to get (or generate)/route trigger signal

uint32 trig_source; // where to take trigger to start acquisition

// <reserved>

uint32 trig_line;

// start trigger mode selection

uint32 trig_start;

// offset of the trigger pulse from nPPS clock\

uint32 trig_delay;

//

(microseconds)

uint32 trig_period_ms; // period in ms to issue start trigger

uint32 trig_stop; // source for the stop trigger

uint32 trig_duration; // milliseconds before issuing stop trigger of

// milliseconds before issuing stop trigger or N-count

// destination to route signals: from SYNC lines or to the outside SyncOut0/1

uint32 clclk_dest[DQL_SYNC_LINES]; // where to feed CL clock

uint32 pps_dest;

// where to feed 1PPS clock to

uint32 trig_dest;

// where to feed start/stop trigger

```

} DQ\_SYNC\_SCHEME, \*pDQ\_SYNC\_SCHEME;

2.2.2

Section A:

Section A parameters describe synchronization source set up information.

IOM SYNC

All IOMs that are PPS / PTP synchronized, whether they are the master 1PPS server or a slave chassis, need to initialize parameters described below in Table 2-1.

| Element Name | Description & Options                                                                                                                                                                                                                           |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| sync_device  | Identifies what type of IOM this structure is used to program.                                                                                                                                                                                  |  |

|              | Set sync_device to any of the following:                                                                                                                                                                                                        |  |

|              | <ul> <li>DQ_SYNC_8347: standard 8347 CPU (PPCx-1G Cube or RACK)</li> <li>DQ_SYNC_5200: standard 5200 CPU (PPCx Cube)</li> <li>DQ_SYNC_8347S: 8347 CPU with 1588 support hardware (-02 or -03 Cube or RACK)</li> </ul>                           |  |

|              | <ul> <li>DQ_SYNC_5200S: <reserved></reserved></li> </ul>                                                                                                                                                                                        |  |

| sync_source  | Sets external input pin on the 10-pin connector that receives nPPS pulse.                                                                                                                                                                       |  |

|              | Set sync_source to any of the following:                                                                                                                                                                                                        |  |

|              | <ul> <li>0 for PTP synchronization</li> <li>DQ_SYNCCLK_SYNCIN0: Uses Syncln0 (5200 or 8347) (pin 10)</li> <li>DQ_SYNCCLK_SYNCIN1: Uses Syncln1 (8347 only) (pin 6)</li> <li>See Figure 1-2 on page 8 for pin descriptions.</li> </ul>           |  |

| sync_line    | Sets internal bus SYNC line that routes the nPPS signal to the ADPLL.                                                                                                                                                                           |  |

|              | Set sync_line to any of the following:                                                                                                                                                                                                          |  |

|              | <ul> <li>0 for PTP synchronization</li> <li>DQ_SYNCCLK_SYNC0: Sync0 line delivers nPPS clock</li> </ul>                                                                                                                                         |  |

|              | <ul> <li>DQ_SYNCCLK_SYNC1: Sync1 line delivers nPPS clock</li> </ul>                                                                                                                                                                            |  |

|              | <ul> <li>DQ_SYNCCLK_SYNC2: Sync2 line delivers nPPS clock</li> </ul>                                                                                                                                                                            |  |

|              | DQ_SYNCCLK_SYNC3: Sync3 line delivers nPPS clock                                                                                                                                                                                                |  |

| sync_mode    | Defines how (or which protocol is used) to synchronize the chassis.                                                                                                                                                                             |  |

|              | <ul> <li>DQ_SYNCCLK_SYNC: synchronized with external PPS pulse</li> <li>DQ_SYNCCLK_NTP: <reserved></reserved></li> </ul>                                                                                                                        |  |

|              | <ul> <li>DQ_SYNCCLK_1588: synchronized with IEEE-1588 PTP protocol.<br/>Logically OR with DQ_SYNCCLK_ETH0 or DQ_SYNCCLK_ETH1 to configure<br/>NIC port to use (e.g., DQ_SYNCCLK_1588   DQ_SYNCCLK_ETH0).<br/>Eth0 (NIC1) is default.</li> </ul> |  |

|              | 1588 (PTP) can only be used when sync_device is DQ_SYNC_8347S and with -02 or -03 Cube or RACK chassis                                                                                                                                          |  |

| nPPS         | Determines the number of pulses per second in the nPPS reference.                                                                                                                                                                               |  |

|              | <ul> <li>Set nPPS to the number of pulses / second. (1 is typical – it will define a 1PPS signal)</li> </ul>                                                                                                                                    |  |

#### Table 2-1 Descriptions for Section A: IOM SYNC Source Configuration

May 2018

| Element Name | Description & Options                                                                                                                                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nPPS_us      | Sets the expected accuracy of the nPPS source. The ADPLL uses this to validate the incoming nPPS pulse and ignores pulses outside this range. The ADPLL will maintain an internal nPPS signal while the reference nPPS input is out of the nPPS_us range. |

|              | Set nPPS_us to the accuracy of the device generating the sync pulse. For example, an nPPS pulse produced by a chassis acting as the 1PPS master can stay within 100 $\mu$ s accuracy; therefore, nPPS_us should be programmed with a value of 100.        |

|              | As a general rule, program this number to the jitter value of your clock source + 100 $\mu s.$ 0 will use the default value for the mode of operation.                                                                                                    |

Table 2-1 Descriptions for Section A: IOM SYNC Source Configuration

| 2.2.3 | Section B:    | Section B parameters provide options to set the chassis as the 1PPS server                                                             |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

|       | Master Server | (Master server). When the following options are set, the chassis is responsible                                                        |

|       | Configuration | for generating a 1PPS synchronization signal internally and routing it externally to synchronize all chassis configured in the system. |

Master server parameters are described in Table 2-2.

| Element Name | Description & Options                                                                                                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sync_server  | Configures the chassis to generate a synchronization signal (1PPS) which can be routed externally to synchronize all chassis in the system.                                                                                        |

|              | A chassis configured as a sync server will generate the 1PPS pulse. Other protocols are currently <reserved>.</reserved>                                                                                                           |

|              | Set sync_server to either of the following:                                                                                                                                                                                        |

|              | <ul> <li>DQ_SYNCSRV_1PPS to configure the chassis as the 1PPS master</li> <li>0 to leave chassis as 1PPS slave or for PTP synchronization</li> </ul>                                                                               |

|              | <b>NOTE</b> that the srv_param element below contains additional information about how to route the signal.                                                                                                                        |

| srv_param    | Controls where the internally generated 1PPS signal will be routed when sync_server is set to DQ_SYNCSRV_1PPS.                                                                                                                     |

|              | Set srv_param to any of the following:                                                                                                                                                                                             |

|              | <ul> <li>DQ_SYNCSRV_SYNCOUT0: Routes to SyncOut0 (5200 or 8347) (pin 8)</li> <li>DQ_SYNCSRV_SYNCOUT1: Routes to SyncOut1 (8347 only) (pin 4)</li> <li>0: set to 0 if chassis is a 1PPS slave or for PTP synchronization</li> </ul> |

|              | Additionally, srv_param can be logically ORed with any of the following to route the 1PPS onto internal SYNC bus:                                                                                                                  |

|              | <ul> <li>DQ_USE_SYNC0: Raw 1PPS to SYNC0</li> <li>DQ_USE_SYNC1: Raw 1PPS to SYNC1</li> <li>DQ_USE_SYNC2: Raw 1PPS to SYNC2</li> <li>DQ_USE_SYNC3: Raw 1PPS to SYNC3</li> </ul>                                                     |

|              | For example, the following routes the 1PPS externally to SyncOut0 on the 10-<br>pin sync connector and internally to SYNC line 0.<br>DQ_SYNCSRV_SYNCOUT0   DQ_USE_SYNC0                                                            |

| trig_server  | Reserved, set to 0.                                                                                                                                                                                                                |

| Table 2-2 Descri | ptions for Section | n B: Master | <sup>c</sup> Configuration |

|------------------|--------------------|-------------|----------------------------|

|------------------|--------------------|-------------|----------------------------|

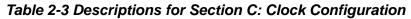

| 2.2.4 | Section C:<br>Clock | Section C parameters provide options for configuring clocks, (e.g., clock routing over SYNC lines and setting clock frequency).                                                                    |

|-------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Configuration       | Each of the parameters in this section is an array of four with one element mapped to each SYNC line. Array element 0 corresponds to SYNC line 0 while array element 3 corresponds to SYNC line 3. |

|       |                     | Clock parameters are described below in Table 2-3.                                                                                                                                                 |

**NOTE:** Typically the SYNC lines are also used to carry an nPPS signal and a trigger. The array elements corresponding to these lines should be left as '0'.

| Element Name | Description & Options                                                                                                                                                                                                                                                                                                  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clock_src[4] | Routes a particular clock source to the corresponding SYNC line. The SYNC line is determined by the element position of the array { <syncline0>, <syncline1>, <syncline2>, <syncline3>} or alternatively set by bitwise ORing a DQ_USE_SYNCx value with the value set.</syncline3></syncline2></syncline1></syncline0> |

|              | The following represent clock sources:                                                                                                                                                                                                                                                                                 |

|              | • DQ_CLOCKSRC_UNUSED: Not connected to any of the following clock sources or connected elsewhere (or left unused)                                                                                                                                                                                                      |

|              | • <dq_clocksrc_adpll: 1pps="" adpll,="" debug="" for="" from="" locked="" only=""></dq_clocksrc_adpll:>                                                                                                                                                                                                                |

|              | DQ_CLOCKSRC_EM0: Clock synthesized by Event Module                                                                                                                                                                                                                                                                     |

|              | • DQ_CLOCKSRC_EM1: Event Module divider 1 clock (use clock_div as divider)                                                                                                                                                                                                                                             |

|              | • DQ_CLOCKSRC_EM2: Event Module divider 2 clock (use clock_div as divider)                                                                                                                                                                                                                                             |

|              | • DQ_CLOCKSRC_SYNCIN0: Clock input from SYNCIN0 pin (5200 or 8347 CPU)                                                                                                                                                                                                                                                 |

|              | DQ_CLOCKSRC_SYNCIN1: Clock input from SYNCIN1 pin (8347 CPU board)                                                                                                                                                                                                                                                     |