# **UEI Test Adapters User Manual**

**Test Adapters for PowerDNx Boards**

**July 2021**

**PN Man-Test-Adapters**

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form by any means, electronic, mechanical, by photocopying, recording, or otherwise without prior written permission.

Information furnished in this manual is believed to be accurate and reliable. However, no responsibility is assumed for its use, or for any infringement of patents or other rights of third parties that may result from its use.

All product names listed are trademarks or trade names of their respective companies.

See the UEI website for complete terms and conditions of sale:

http://www.ueidaq.com/cms/terms-and-conditions

### **Contacting United Electronic Industries:**

Mailing Address:Shipping Address:249 Vanderbilt Avenue24 Morgan DriveNorwood, MA 02062Norwood, MA 02062

U.S.A. U.S.A.

For a list of our distributors and partners in the US and around the world, please contact a member of our support team:

Support:

Telephone: (508) 921-4600 Fax: (508) 668-2350

Also see the FAQs and online "Live Help" feature on our web site.

**Internet Support:**

Support:support@ueidaq.comWebsite:www.ueidaq.comFTP Site:ftp://ftp.ueidaq.com

#### **Product Disclaimer:**

#### **WARNING!**

### DO NOT USE PRODUCTS SOLD BY UNITED ELECTRONIC INDUSTRIES, INC. AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

Products sold by United Electronic Industries, Inc. are not authorized for use as critical components in life support devices or systems. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Any attempt to purchase any United Electronic Industries, Inc. product for that purpose is null and void and United Electronic Industries Inc. accepts no liability whatsoever in contract, tort, or otherwise whether or not resulting from our or our employees' negligence or failure to detect an improper purchase.

Specifications in this document are subject to change without notice. Check with UEI for current status.

### **Table of Contents**

| Introduc     | ction 1                                               |

|--------------|-------------------------------------------------------|

| 1.1          | Overview                                              |

| 1.2          | Organization of this Manual1                          |

| 1.3          | Manual Conventions                                    |

| 1.4          | Before You Begin 1                                    |

| 1.5          | Related Resources                                     |

| 101 Tes      | t Adapter3                                            |

| 2.1          | General Description                                   |

| 2.2          | Analog I/O Loopback                                   |

| 2.3          | Industrial Digital I/O Loopback5                      |

| 2.4          | TTL Digital I/O Loopback6                             |

| 2.5          | Serial Loopback6                                      |

| 2.6<br>2.6.1 | I2C Port Testing.   6     Temperature Data Format   7 |

| 2.7          | Pinout8                                               |

| 2.8          | Using the 101 Test Adapter8                           |

| 2.9          | Specifications                                        |

| 201 Tes      | t Adapter                                             |

| 3.1          | General Description                                   |

| 3.2          | Device Architecture                                   |

| 3.3          | Using the 201 Test Adapter12                          |

| 3.4          | Specifications                                        |

| 201-to-3     | 08 Test Adapter                                       |

| 4.1          | Features                                              |

| 4.2          | General Description                                   |

| 4.3          | Device Architecture                                   |

| 4.4          | Using the 201-to-308 Test Adapter                     |

| 4.5          | Specifications                                        |

| 202 Tes      | t Adapter                                             |

| 5.1          | General Description                                   |

| 5.2          | Device Architecture                                   |

| 5.3          | Using the 202 Test Adapter                            |

| 5.4          | Specifications                                        |

| 205 Tes      | t Adapter                                             |

| 6.1     | General Description               | . 24 |

|---------|-----------------------------------|------|

| 6.2     | Device Architecture               | . 24 |

| 6.3     | Using the 205 Test Adapter        | . 25 |

| 6.4     | Specifications                    | . 26 |

| 207/217 | Test Adapter                      | . 27 |

| 7.1     | General Description               | . 27 |

| 7.2     | Device Architecture               | . 28 |

| 7.3     | Using the 207/217 Test Adapter    | . 29 |

| 7.4     | Specifications                    | . 30 |

| 207-to- | 332 Test Adapter                  | . 31 |

| 8.1     | Features                          | . 31 |

| 8.2     | General Description               | . 31 |

| 8.3     | Device Architecture               | . 33 |

| 8.4     | Using the 207-to-332 Test Adapter | . 34 |

| 8.5     | Specifications                    | . 35 |

| 208 Tes | st Adapter                        | . 36 |

| 9.1     | General Description               | . 36 |

| 9.2     | Device Architecture               | . 37 |

| 9.3     | Using the 208 Test Adapter        | . 38 |

| 9.4     | Specifications                    | . 39 |

| 211 Tes | st Adapter                        | . 40 |

| 10.1    | Features                          | . 40 |

| 10.2    | General Description               | . 40 |

| 10.3    | Device Architecture               | . 41 |

| 10.4    | Using the 211 Test Adapter        | . 42 |

| 10.5    | Specifications                    | . 43 |

| 225 Tes | st Adapter                        | . 44 |

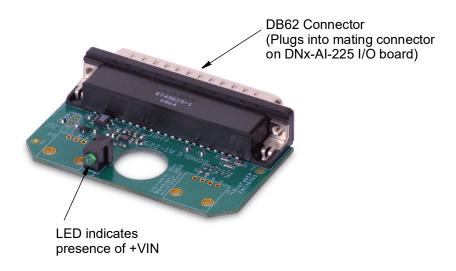

| 11.1    | General Description               | . 44 |

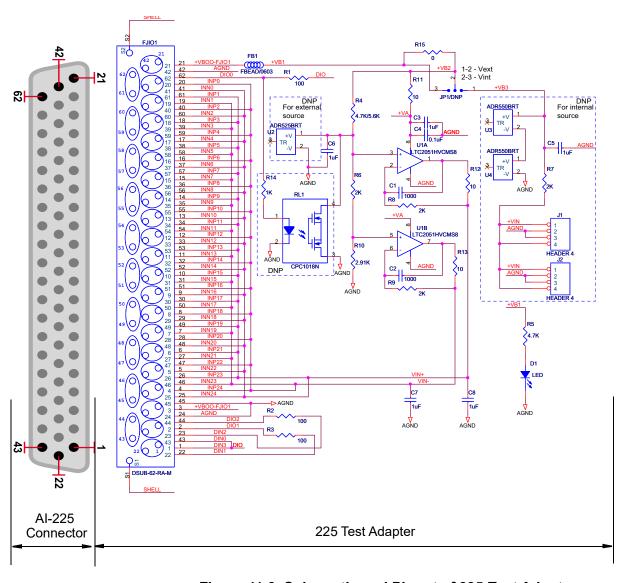

| 11.2    | Device Architecture               | . 45 |

| 11.3    | Using the 225 Test Adapter        | . 46 |

| 11.4    | Specifications                    | . 47 |

| 254 Tes | st Adapter                        | . 48 |

| 12.1    | Features                          | . 48 |

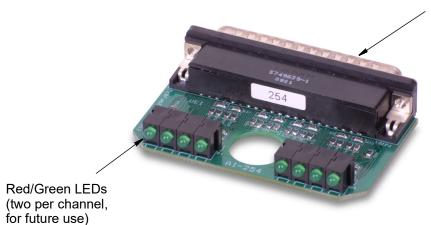

| 12.2    | General Description               | . 48 |

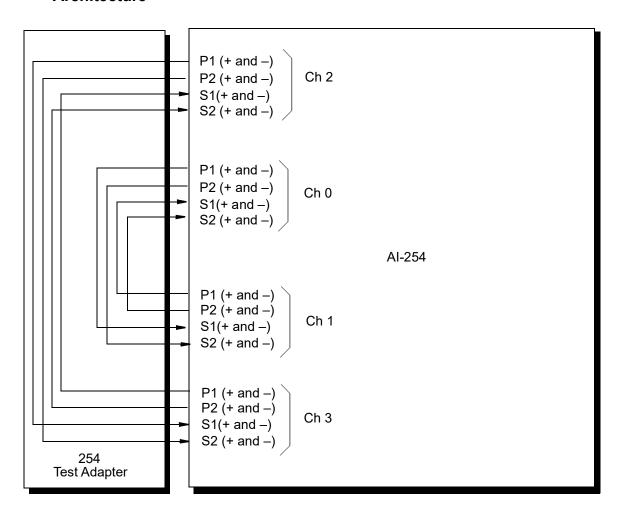

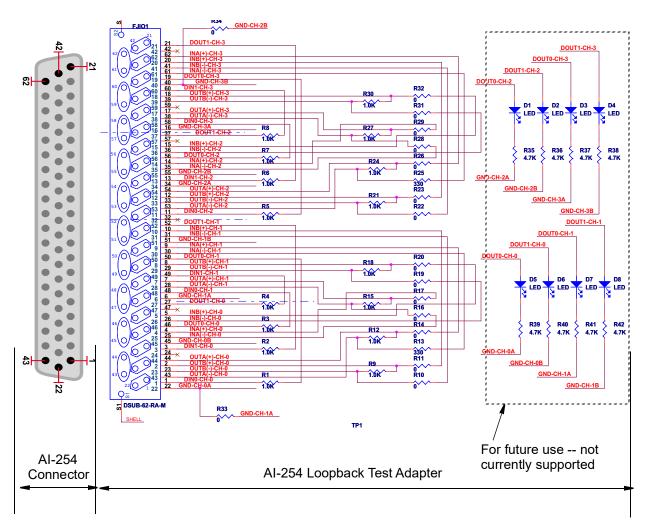

| 12.3    | Device Architecture               | . 49 |

| 12.4     | Using the 254 Test Adapter         | 50 |

|----------|------------------------------------|----|

| 12.5     | Specifications                     | 51 |

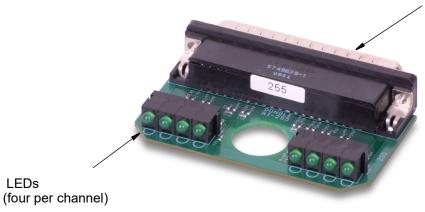

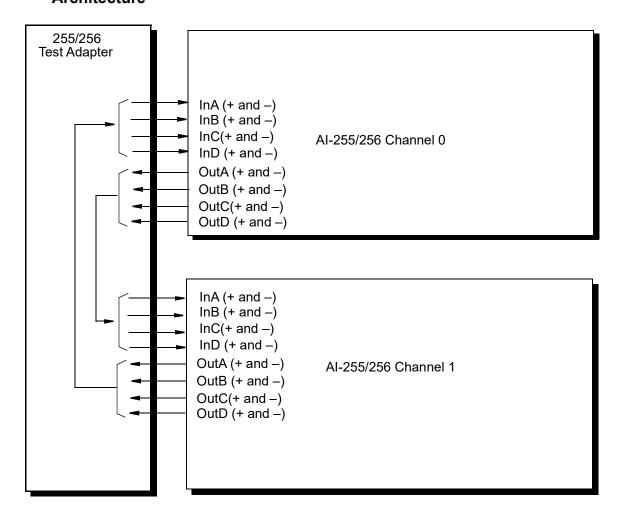

| 255/256  | Test Adapter                       | 52 |

| 13.1     | Features                           | 52 |

| 13.2     | General Description                | 52 |

| 13.3     | Device Architecture                | 53 |

| 13.4     | Using the 255/256 Test Adapter     | 54 |

| 13.5     | Specifications                     | 55 |

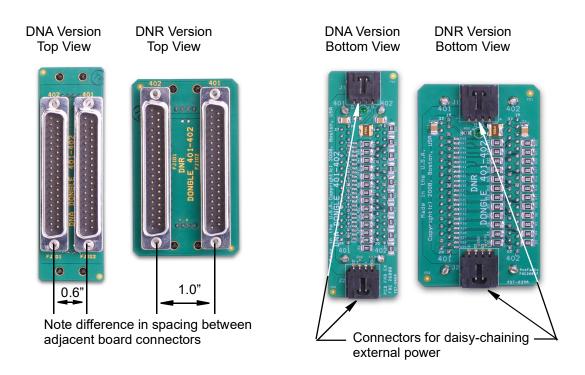

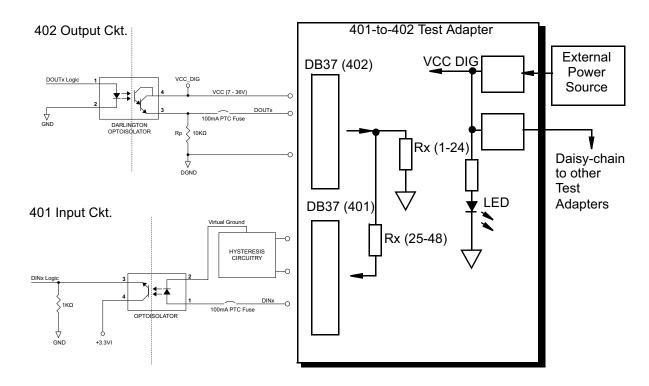

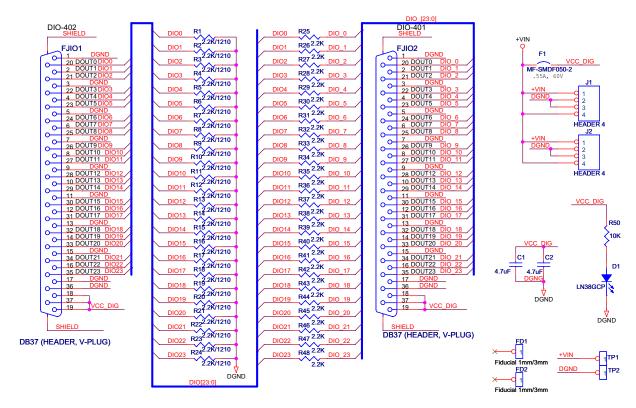

| 401-to-4 | 02 Test Adapter                    | 56 |

| 14.1     | General Description                | 56 |

| 14.2     | Device Architecture                | 57 |

| 14.3     | Using the 401-to-402 Test Adapter  | 58 |

| 14.4     | Specifications                     | 59 |

| 403 Test | t Adapter                          | 60 |

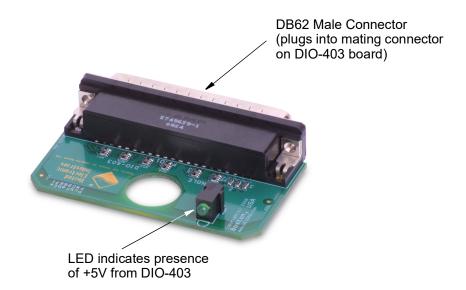

| 15.1     | General Description                | 60 |

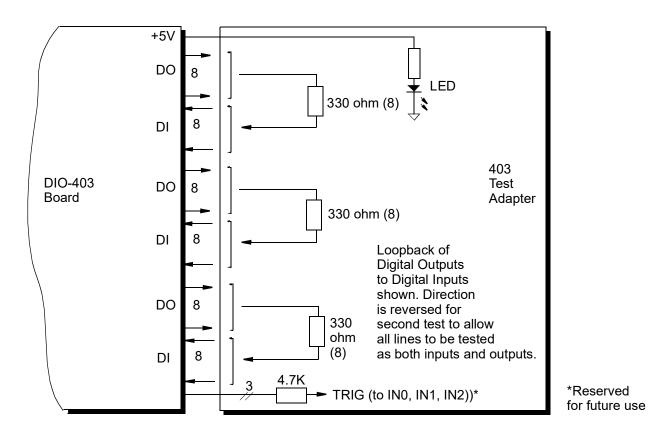

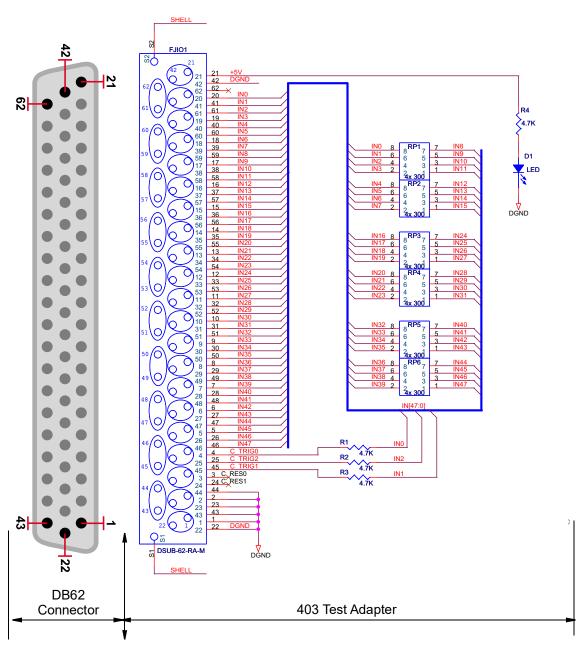

| 15.2     | Device Architecture                | 61 |

| 15.3     | Using the 403 Test Adapter         | 62 |

| 15.4     | Specifications                     | 63 |

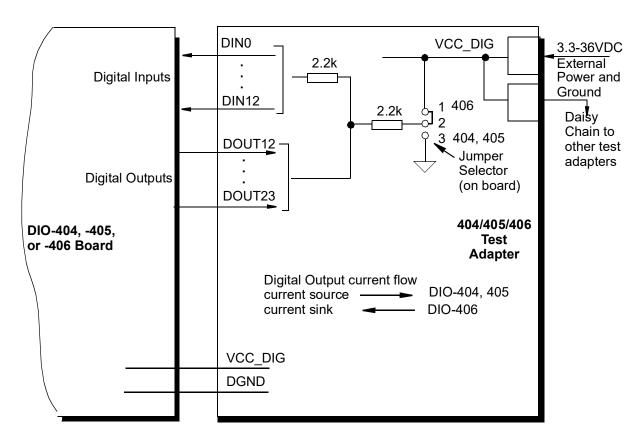

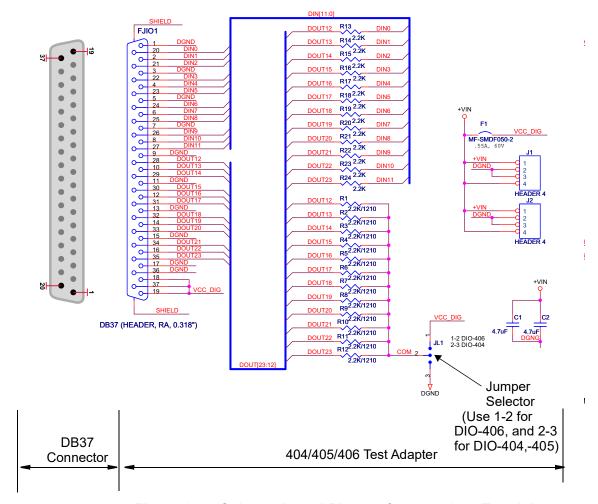

| 404/405/ | 406 Test Adapter                   | 64 |

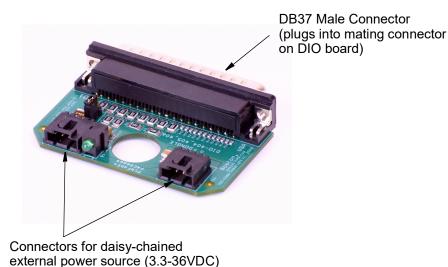

| 16.1     | General Description                | 64 |

| 16.2     | Device Architecture                | 65 |

| 16.3     | Using the 404/405/406 Test Adapter | 66 |

| 16.4     | Specifications                     | 67 |

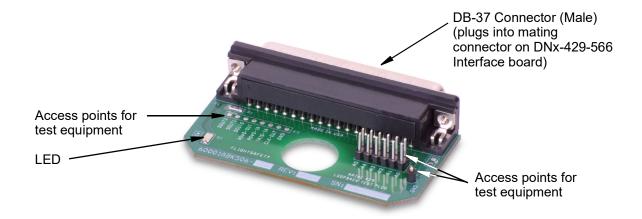

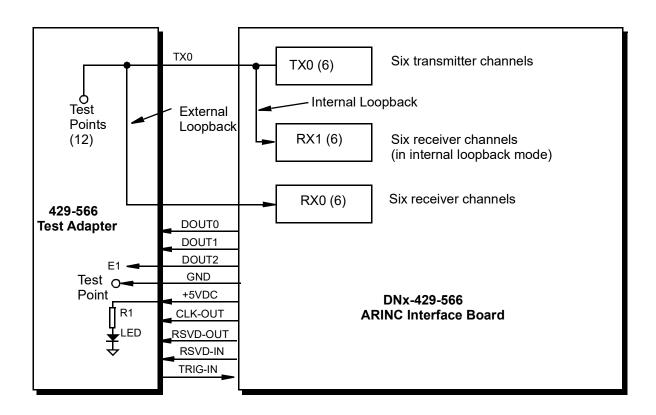

| 429-566  | Test Adapter                       | 68 |

| 17.1     | General Description                | 68 |

| 17.2     | Pinout                             | 71 |

| 17.3     | Using the 429-566 Test Adapter     | 71 |

| 17.4     | Specifications                     | 72 |

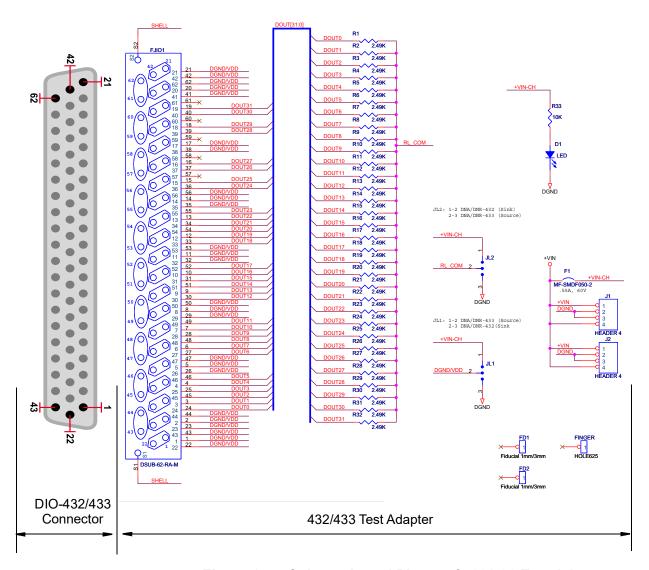

| 432/433  | Test Adapter                       | 73 |

| 18.1     | General Description                | 73 |

| 18.2     | Device Architecture                | 74 |

| 18.3     | Using the 432/433 Test Adapter     | 75 |

| 18.4     | Specifications                     | 76 |

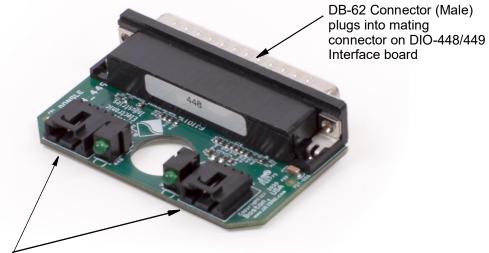

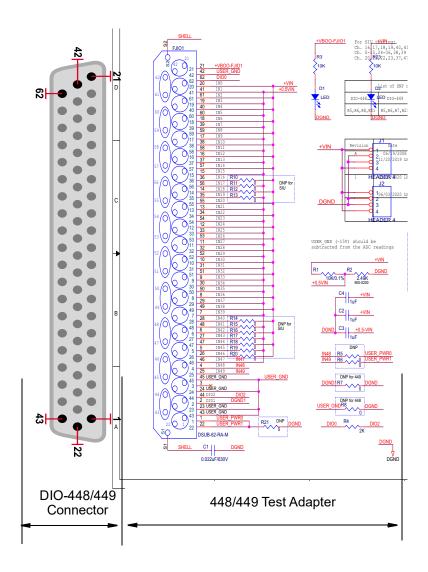

| 448/449  | Test Adapter                       | 77 |

| 19.1     | General Description                | 77 |

| 19.2    | Using the 448/449 Test Adapter | 79  |

|---------|--------------------------------|-----|

| 19.3    | Specifications                 | 80  |

| 501 Tes | st Adapter                     | 81  |

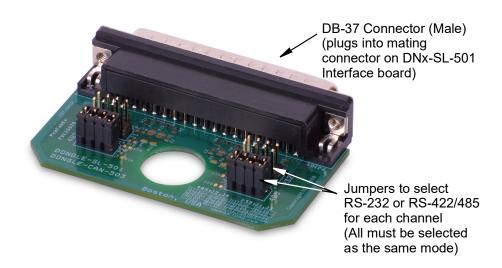

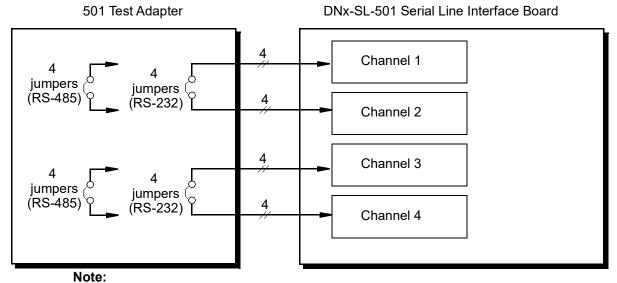

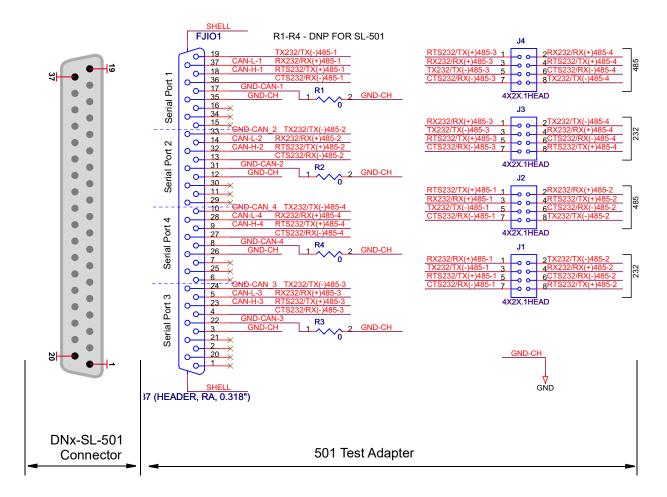

| 20.1    | General Description            | 81  |

| 20.2    | Device Architecture            | 82  |

| 20.3    | Using the 501 Test Adapter     | 83  |

| 20.4    | Specifications                 | 84  |

| 503 Tes | st Adapter                     | 85  |

| 21.1    | General Description            | 85  |

| 21.2    | Using the 503 Test Adapter     | 86  |

| 21.3    | Specifications                 | 87  |

| 508 Tes | st Adapter                     | 88  |

| 22.1    | General Description            | 88  |

| 22.2    | Device Architecture            | 89  |

| 22.3    | Using the 508 Test Adapter     | 90  |

| 22.4    | Specifications                 | 91  |

| 601 Tes | st Adapter                     | 92  |

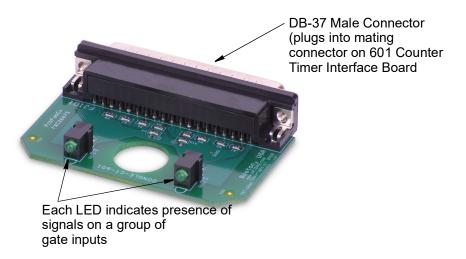

| 23.1    | General Description            | 92  |

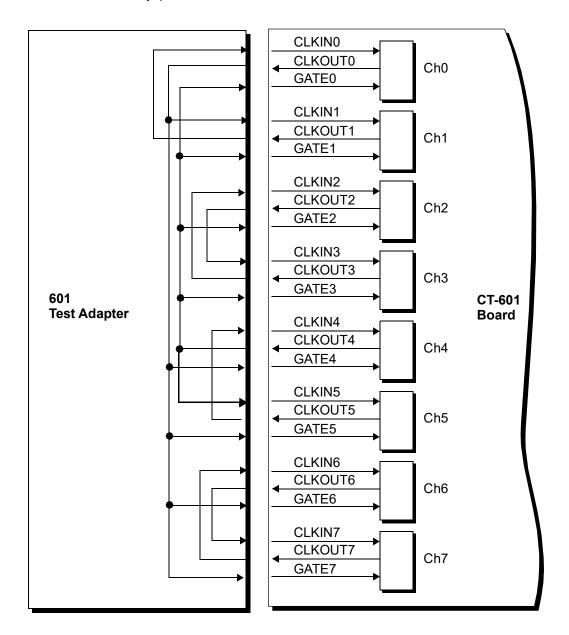

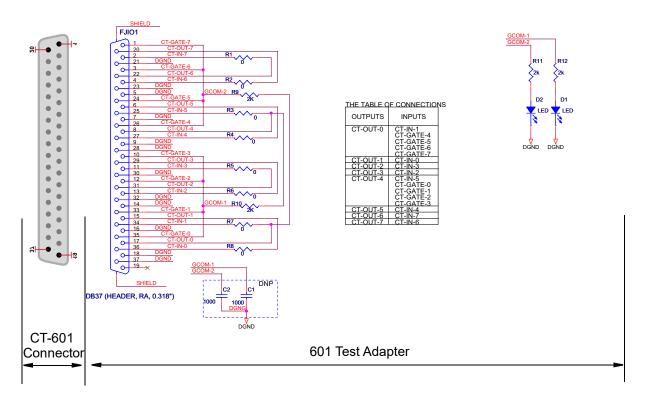

| 23.2    | Device Architecture            | 93  |

| 23.3    | Using the 601 Test Adapter     | 95  |

| 23.4    | Specifications                 | 95  |

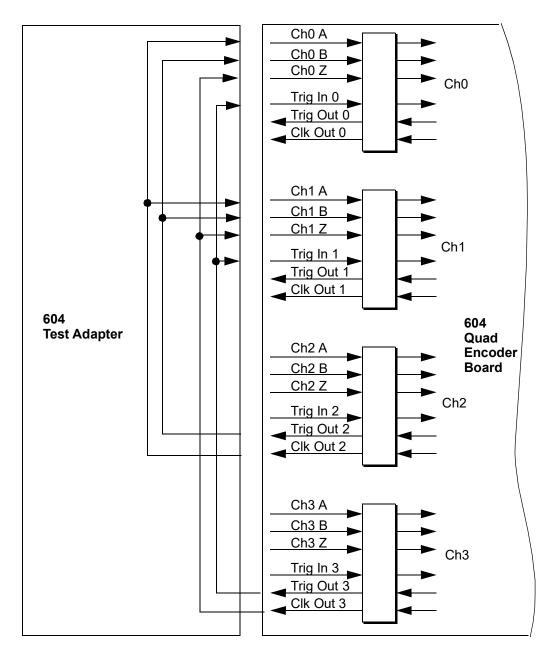

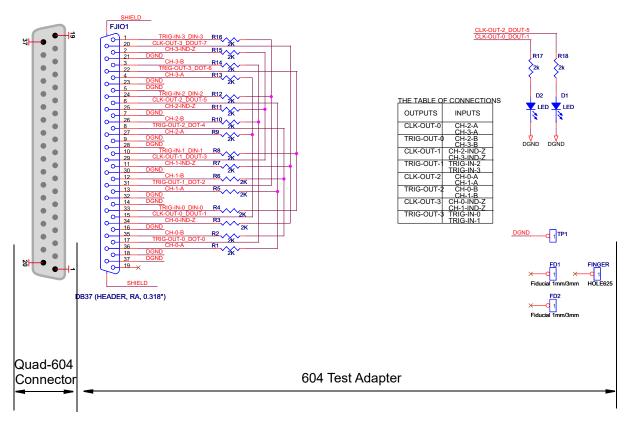

| 604 Tes | st Adapter                     | 96  |

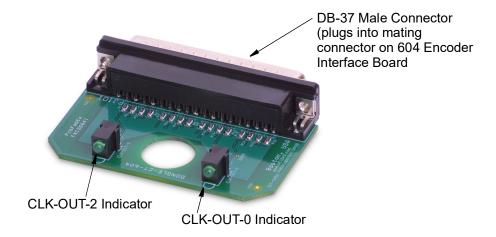

| 24.1    | General Description            | 96  |

| 24.2    | Device Architecture            | 97  |

| 24.3    | Using the 604 Test Adapter     | 99  |

| 24.4    | Specifications                 | 99  |

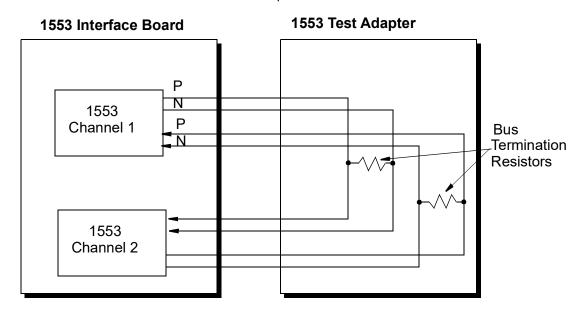

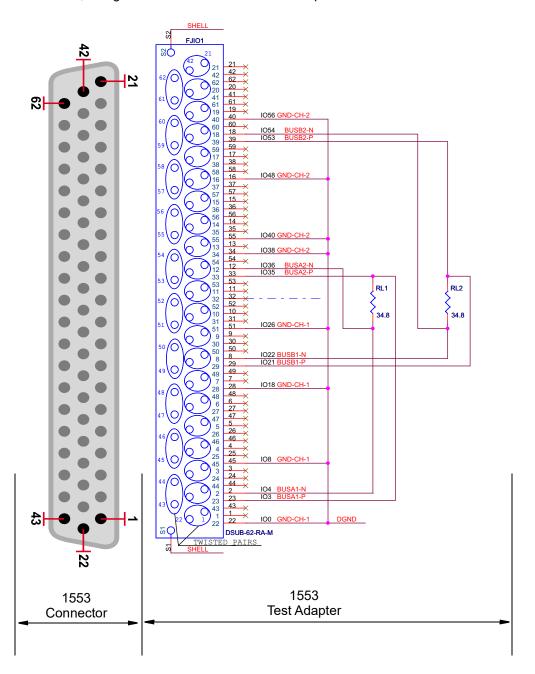

| 1553 Te | est Adapter                    | 100 |

| 25.1    | General Description            | 100 |

| 25.2    | Using the 1553 Test Adapter    | 102 |

| 25.3    | Specifications                 | 103 |

### **List of Figures**

|                                                             | Introduction                                                                                                                                                                                                                                                                                                                                |          |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9 | 101 Test Adapter Photo of 101 Test Adapter Schematic of Analog Loopback Channel Industrial Digital I/O Channel Configuration External Power Supply Connector TTL Digital I/O Channel Configuration Schematic of Serial Port Loopback Circuit Schematic of I2C Port Test Circuit Example Data from ADT7420 Pinout of DNx-TADP-101 and MF-101 |          |

| 3-1<br>3-2<br>3-3                                           | 201 Test Adapter  Photo of 201 Test Adapter  Block Diagram of 201 Test Adapter  Schematic of 201 Test Adapter                                                                                                                                                                                                                               | 10<br>11 |

| 4-1<br>4-2<br>4-3                                           | 201-to-308 Test Adapter  Photo of 201-to-308 Test Adapter  Block Diagram of 201-to-308 Test Adapter  Schematic of 201-to-308 Test Adapter                                                                                                                                                                                                   | 15<br>16 |

| 5-1<br>5-2<br>5-3                                           | 202 Test Adapter  Photo of 202 Test Adapter  Block Diagram of 202 Test Adapter  Schematic and Pinout of 202 Test Adapter                                                                                                                                                                                                                    | 20<br>21 |

| 6-1<br>6-2                                                  | 205 Test Adapter                                                                                                                                                                                                                                                                                                                            | 24       |

| 7-1<br>7-2<br>7-3                                           | 207/217 Test Adapter Photo of 207/217 Test Adapter Block Diagram of 207/217 Test Adapter Schematic of 207/217 Test Adapter                                                                                                                                                                                                                  | 27<br>28 |

| 8-1<br>8-2<br>8-3                                           | 207-to-332 Test Adapter Photo of 207-to-332 Test Adapter Block Diagram of 207-to-332 Test Adapter Schematic and Pinout of 207-to-332 Test Adapter                                                                                                                                                                                           | 31<br>33 |

| 9-1<br>9-2<br>9-3                                           | 208 Test Adapter  Photo of 208 Test Adapter  Block Diagram of 208 Test Adapter  Schematic and Pinout of 208 Test Adapter                                                                                                                                                                                                                    | 36<br>37 |

| 10-1<br>10-2<br>10-3                                        | 211 Test Adapter                                                                                                                                                                                                                                                                                                                            | 40<br>41 |

| 11-1<br>11-2                                                | 225 Test Adapter Photo of 225 Test Adapter Schematic and Pinout of 225 Test Adapter                                                                                                                                                                                                                                                         | 44       |

| 12-1                         | <b>254 Test Adapter</b> Photo of 254 Test Adapter                                                                                                                     |          |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 12-2<br>12-3                 | Channel Configuration of 254 Test Adapter                                                                                                                             |          |

| 13-1<br>13-2<br>13-3         | 255/256 Test Adapter Photo of 255/256 Test Adapter Channel Configuration of 255/256 Test Adapter Schematic and Pinout of 255/256 Test Adapter                         | 52       |

| 14-1<br>14-2<br>14-3         | 401-to-402 Test Adapter  Photo of 401-to-402 Test Adapter  Block Diagram of 401-to-402 Test Adapter  Schematic and Pinout of 401-to-402 Test Adapter                  | 56<br>56 |

| 15-1<br>15-2<br>15-3         | 403 Test Adapter Photo of 403 Test Adapter Block Diagram of 403 Test Adapter Schematic and Pinout of 403 Test Adapter                                                 | 60<br>61 |

| 16-1<br>16-2<br>16-3         | 404/405/406 Test Adapter Photo of 404/405/406 Test Adapter Block Diagram of 404/405/406 Test Adapter Schematic and Pinout of 404/405/406 Test Adapter                 | 64<br>65 |

| 17-1<br>17-2<br>17-3<br>17-4 | 429-566 Test Adapter Photo of 429-566 Test Adapter Block Diagram of 429-566 Test Adapter Schematic of the 429-566 Test Adapter Pinout of 429-566 Test Adapter         | 68<br>69 |

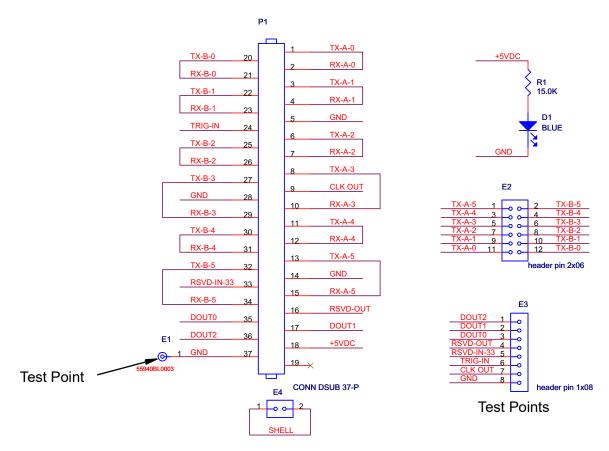

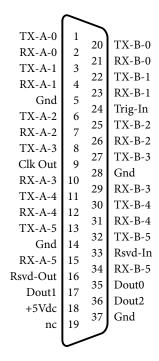

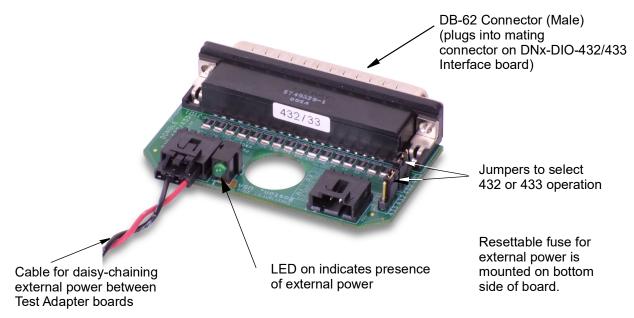

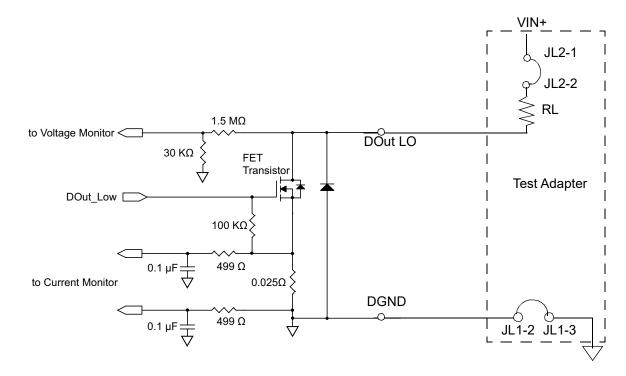

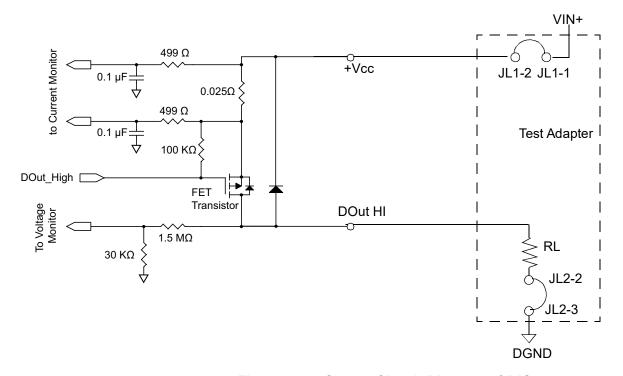

| 18-1<br>18-2<br>18-3<br>18-4 | 432/433 Test Adapter Photo of 432/433 Test Adapter Output Circuit Diagram of DIO-432. Output Circuit Diagram of DIO-433. Schematic and Pinout of 432/433 Test Adapter | 73<br>74 |

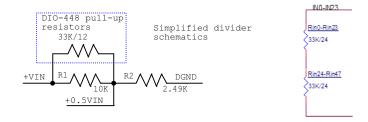

| 19-1<br>19-2<br>19-3         | 448/449 Test Adapter Photo of 448/449 Test Adapter Schematic and Pinout of 448/449 Test Adapter Divider Circuit on Odd Channels                                       | 77       |

| 20-1<br>20-2<br>20-3         | 501 Test Adapter Photo of 501 Test Adapter Block Diagram of 501 Test Adapter Schematic of 501 Test Adapter                                                            | 81       |

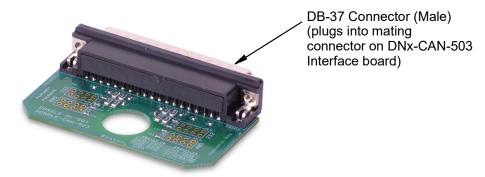

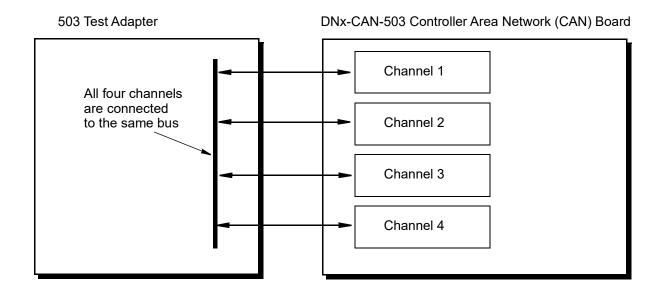

| 21-1<br>21-2<br>21-3         | 503 Test Adapter Photo of 503 Test Adapter Block Diagram of 503 Test Adapter Schematic of 503 Test Adapter                                                            | 85       |

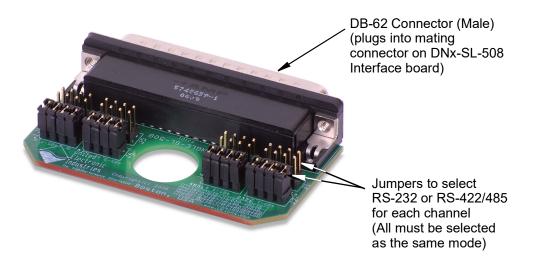

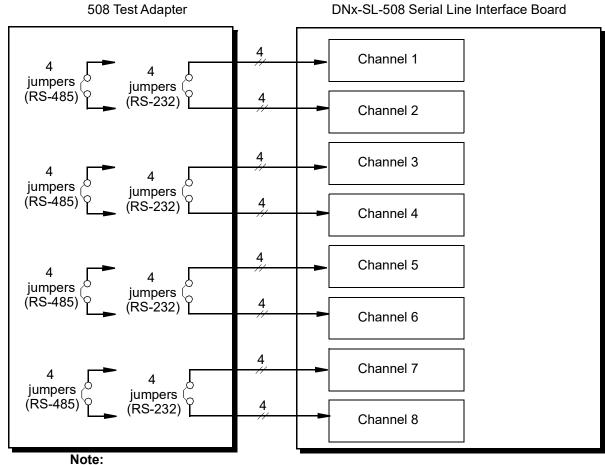

| 22-1<br>22-2<br>22-3         | 508 Test Adapter  Photo of 508 Test Adapter  Block Diagram of 508 Test Adapter  Schematic of 508 Test Adapter                                                         | 88<br>28 |

|                              | 601 Test Adapter                                                                                                                                                      | 92       |

| 23-1 | Photo of 601 Test Adapter                               | 92  |

|------|---------------------------------------------------------|-----|

| 23-2 | Connection Diagram of CT-601 Board and 601 Test Adapter | 93  |

| 23-3 | Schematic of 601 Test Adapter                           |     |

|      | 604 Test Adapter                                        | 96  |

| 24-1 | Photo of 604 Test Adapter                               |     |

| 24-2 | Connection Diagram of QUAD-604 and 604 Test Adapter     | 97  |

| 24-3 | Schematic of 604 Test Adapter                           | 98  |

|      | 1553 Test Adapter                                       | 100 |

| 25-1 | Photo of 1553 Test Adapter                              | 100 |

| 25-2 | Block Diagram of 1553 Test Adapter                      | 101 |

| 25-3 | Schematic of 1553 Test Adapter                          | 102 |

|      |                                                         |     |

### **List of Tables**

|            | Introduction                                                                            | . 1 |

|------------|-----------------------------------------------------------------------------------------|-----|

| 2-1<br>2-2 | 101 Test Adapter                                                                        | 4   |

| 3-1        | <b>201 Test Adapter</b>                                                                 |     |

| 4-1        | <b>201-to-308 Test Adapter</b> Technical Specifications                                 |     |

| 5-1        | <b>202 Test Adapter</b>                                                                 |     |

| 6-1        | <b>205 Test Adapter</b>                                                                 |     |

| 7-1        | <b>207/217 Test Adapter</b> Technical Specifications for the 207/217 Test Adapter       |     |

| 8-1        | <b>207-to-332 Test Adapter</b> Technical Specifications                                 |     |

| 9-1        | <b>208 Test Adapter</b>                                                                 |     |

| 10-1       | <b>211 Test Adapter</b> Technical Specifications for the 211 Test Adapter               |     |

| 11-1       | <b>225 Test Adapter</b> Technical Specifications for the 225 Test Adapter               |     |

| 12-1       | <b>254 Test Adapter</b> Technical Specifications (when used with the Al-254)            |     |

| 13-1       | 255/256 Test Adapter Technical Specifications                                           |     |

| 14-1       | <b>401-to-402 Test Adapter</b> Technical Specifications for the 401-to-402 Test Adapter |     |

| 15-1       | 403 Test Adapter Technical Specifications for the 403 Test Adapter                      |     |

| 16-1       | 404/405/406 Test Adapter                                                                |     |

| 17-1       | <b>429-566 Test Adapter</b> Technical Specifications for the 429-566 Test Adapter       |     |

| 18-1       | 432/433 Test Adapter Technical Specifications for the 432/433 Test Adapter              |     |

| 19-1       | 448/449 Test Adapter  Technical Specifications for the 448/449 Test Adapter             |     |

| 20-1       | <b>501 Test Adapter</b> Technical Specifications for the 501 Test Adapter               |     |

|            | 503 Test Adapter                                                                        | 85  |

| 21-1 | Technical Specifications for the 503 Test Adapter  | 87  |

|------|----------------------------------------------------|-----|

|      | 508 Test Adapter                                   | 88  |

| 22-1 | Technical Specifications for the 508 Test Adapter  | 91  |

|      | 601 Test Adapter                                   | 92  |

| 23-1 | Source and Destination of Channel Signals          |     |

| 23-2 | Technical Specifications for the 601 Test Adapter  |     |

|      | 604 Test Adapter                                   | 96  |

| 24-1 | Source and Destination of Channel Signals          |     |

| 24-2 | Technical Specifications for the 604 Test Adapter  | 99  |

|      | 1553 Test Adapter                                  | 100 |

| 25-1 | Technical Specifications for the 1553 Test Adapter | 103 |

### Introduction

#### 1.1 Overview

This manual describes the design and functional operation of UEI's test adapters. Test adapters are used for preliminary testing and troubleshooting of UEI I/O boards.

A quick reference guide for the test adapters may be downloaded from UEI's website at <a href="https://www.ueidaq.com/products/uei-test-adapters">https://www.ueidaq.com/products/uei-test-adapters</a>.

#### 1.2 Organization

Each chapter is dedicated to a specific test adapter and titled with the name(s) of this Manual of the associated I/O board(s). Chapters are arranged in the manual according to I/O board number.

#### 1.3 Manual Conventions

The following conventions are used throughout this manual:

Tips are designed to highlight quick ways to get the job done or to reveal good ideas you might not discover on your own.

CAUTION! advises you of precautions to take to avoid injury, data loss, and damage to your boards or a system crash.

**NOTE:** Notes alert you to important information.

| Typeface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                              | Example                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------|

| bold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | field or button names                    | Click Scan Network           |

| »                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | hierarchy to get to a specific menu item | File » New                   |

| fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | source code to be entered verbatim       | session.CleanUp()            |

| <br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br><br> | placeholder for user-defined text        | pdna:// <ip address=""></ip> |

| italics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | path to a file or directory              | C:/Program Files             |

#### 1.4 **Before You** Begin

#### No Hot Swapping!

Before plugging any I/O connector into the Cube or Rack, be sure to remove power from all field wiring. Failure to do so may cause severe damage to the equipment.

#### Check Your Firmware

Ensure that the firmware installed on the Cube or Rack CPU matches the UEI software version installed on your PC. The IOM is shipped with pre-installed firmware and a matching software installation. If you upgrade your software installation, you must also update the firmware on your Cube or Rack CPU. Instructions for updating firmware are provided in the UEI chassis user manuals.

## 1.5 Related Resources

For information about the I/O board associated with each test adapter, please refer to the website or the documentation folder included with the software installation. On Windows, these resources can be found from the desktop by clicking **Start** » **All Program** » **UEI**.

UEI's website includes other user resources such as application notes, FAQs, tutorials, and videos. In particular, the glossary of terms may be helpful when reading through this manual: <a href="https://www.ueidag.com/glossary">https://www.ueidag.com/glossary</a>

Additional questions? Please email UEI Support at <a href="mailto:support@ueidaq.com">support@ueidaq.com</a> or call 508-921-4600.

### 101 Test Adapter

The 101 Test Adapter (p/n DNx-TADP-101) is an accessory designed for testing UEI's DNx-MF-101 Multifunction I/O Board.

# 2.1 General Description

Under software control, the 101 Test Adapter facilitates testing of all channels on a DNx-MF-101 Multifunction I/O Board:

- 16 single-ended or 8 fully differential analog inputs

- 2 analog outputs

- 16 industrial digital I/O bits

- 6 TTL digital bits (4 I/O, 1 input, 1 output)

- 1 RS-232/422/485 serial port

- 1 I<sup>2</sup>C port (master and slave)

Loopback tests can be performed between analog inputs and outputs, industrial digital inputs and outputs, TTL inputs and outputs, and serial receiver and transmitter. A built-in ADT7420 temperature sensor is used to verify I<sup>2</sup>C port functionality.

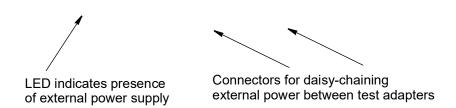

Industrial digital outputs draw power from a user-supplied 0-55V source. If the external supply is disconnected, +VIn is pulled up to an internal +60 V supply by a 2  $M\Omega$  resistor. An on-board LED indicates the status of VIn

#### **PRELIMINARY**

Figure 2-1 Photo of 101 Test Adapter

# 2.2 Analog I/O Loopback

The 101 Test Adapter connects two analog output channels to analog input channels as shown in **Table 2-1**.

Table 2-1 Analog Channel Configuration

| Single-Ended Input | Differential Input | Analog Output |

|--------------------|--------------------|---------------|

| Aln0               | Aln0+              | AOut0         |

| Aln1               | Aln0-              | AOut1         |

| Aln2               | Aln1+              | AOut1         |

| Aln3               | Aln1-              | AOut0         |

| Aln4               | Aln2+              | AOut0         |

| Aln5               | Aln2-              | AOut1         |

| Aln6               | Aln3+              | AOut1         |

| Aln7               | Aln3-              | AOut0         |

| Aln8               | Aln4+              | AOut0         |

| Aln9               | Aln4-              | AOut1         |

| Aln10              | Aln5+              | AOut1         |

| Aln11              | Aln5-              | AOut0         |

| Aln12              | Aln6+              | AOut0         |

| Aln13              | Aln6-              | AOut1         |

| Aln14              | Aln7+              | AOut1         |

| Aln15              | Aln7-              | AOut0         |

Analog outputs can be tested in both voltage and current output mode. In voltage output mode, differential input measurements take the difference of AOout1 and AOut0. For example, setting AOut1 to -5V and AOut0 to +2V should return +7V on AIn6+/- and -7V on AIn7+/-.

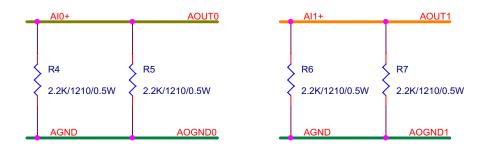

Use single-ended analog inputs to test current output mode. Since each analog pin is tied to ground via a  $2.2k\Omega$  resistor (**Figure 2-2**), the output current I encounters a total resistance of  $1.1k\Omega$ , creating a voltage of I\*1.1k $\Omega$ .

Figure 2-2 Schematic of Analog Loopback Channel

# 2.3 Industrial Digital I/O Loopback

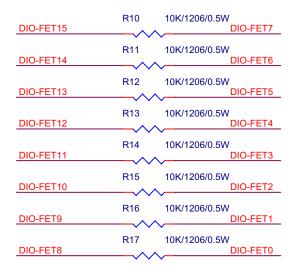

The 101 Test Adapter connects FET-based digital I/O channels 0-7 to channels 8-15 as shown in **Figure 2-3**.

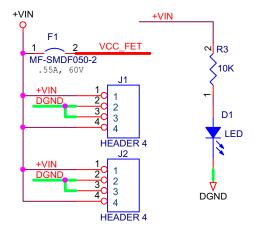

Industrial digital outputs are designed to draw power from an external supply, which is protected by a resettable fuse (**Figure 2-4**). Two power connectors are provided, allowing daisy-chaining of external power to other test adapters. When using the test adapter, all 4 blocks of DIO channels (16 channels total) are connected to the same power supply.

If +Vin is disconnected, the MF-101 automatically pulls up the positive rail to an internal +60 V supply using a 2 M $\Omega$  resistor. The internal supply is only meant to be used for very basic testing and to prevent accidental floating inputs on the MF-101. A disconnected +VIn may cause unexpected digital input readings as the outputs switch ON/OFF.

Figure 2-3 Industrial Digital I/O Channel Configuration

Figure 2-4 External Power Supply Connector

### 2.4 Loopback

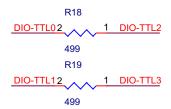

TTL Digital I/O TTL digital I/O channels 0-1 are tied to channels 2-3 as shown in Figure 2-5. TRIGIN reads the TRIGOUT signal.

Figure 2-5 TTL Digital I/O Channel Configuration

#### 2.5 Serial Loopback

The serial port can be tested in either RS-232 or RS-485 mode. As shown in Figure 2-6, TRIGOUT controls the relay that switches between the two modes. Set TRIGOUT=1 to use the port in RS-232 mode, and set TRIGOUT=0 to use RS-422/485 mode. Remember to disable the internal loopback software setting if you want to make use of this external loopback test circuit.

Figure 2-6 Schematic of Serial Port Loopback Circuit

#### 2.6 **I2C Port Testing**

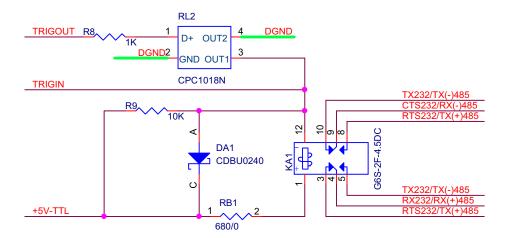

The 101 Test Adapter includes an ADT7420 temperature sensor wired to the I<sup>2</sup>C bus as shown in Figure 2-7. You can use the sensor to test both the MF-101 master module and Bus Monitor slave module. Example programs for reading the temperature sensor are provided in the "Sample101" (low-level C code) and "I2CReadSensor" (high-level C++ code) folders. Note that the I<sup>2</sup>C address of the ADT7420 is set to 0x48.

Figure 2-7 Schematic of I<sup>2</sup>C Port Test Circuit

### 2.6.1 Temperature Data Format

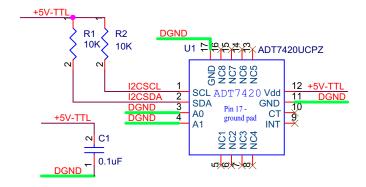

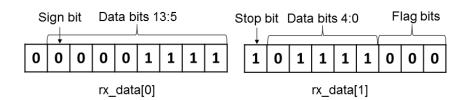

By default, the ADT7420 encodes the temperature in a 13-bit number. Therefore, the MF-101 master should be programmed to read two bytes from the sensor and discard the three LSBs.

An example is illustrated in **Figure 2-8**. If the master receives  $rx_{data[0]=0xf}$  and  $rx_{data[1]=0x178}$ , then the raw temperature data equals 0x1ef (binary:  $0\ 0001\ 1110\ 1111$ , decimal: 495). Data bit 13 indicates whether the temperature is positive or negative. If the temperature is positive, divide the raw temperature data number by 16 to obtain the temperature in °C. In this example, temperature = 495/16 = 30.9 °C. If the sign bit is 1, subtract 8192 from the raw temperature data number before dividing by 16. Refer to the ADT7420 datasheet for additional details on this conversion.

Figure 2-8 Example Data from ADT7420

#### 2.7 Pinout

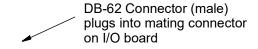

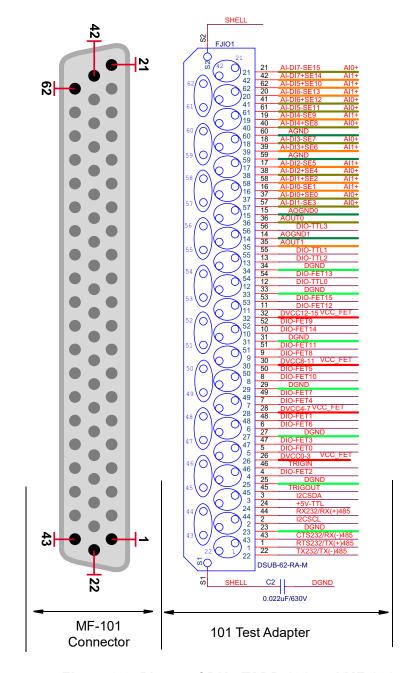

The 101 Test Adapter plugs directly into the DB-62 mating connector of the MF-101. The pinout for the 101 Test Adapter is shown below in **Figure 2-9**.

Figure 2-9 Pinout of DNx-TADP-101 and MF-101

# 2.8 Using the 101 Test Adapter

Testing the DNx-MF-101 Multifunction I/O Board with the DNx-TADP-101 requires you to develop a simple program to acquire data and display the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. Please refer to the DNx-MF-101 User Manual for information about programming the MF-101.

### **2.9 Specifications** Technical specifications for the 101 Test Adapter are listed in **Table 2-2** below.

Table 2-2 Technical Specifications for the DNx-TADP-101

| Channel Configurations      |                                       |  |

|-----------------------------|---------------------------------------|--|

| Analog IO                   | 2 outputs connected to 16 inputs      |  |

| Analog Output Modes         | Voltage or current                    |  |

| Industrial DIO              | DIO15:8 paired with DIO7:0            |  |

| TTL DIO                     | TTL0:1 paired to TTL2:3               |  |

|                             | TRIGIN connected to TRIGOUT           |  |

| Serial Port                 | Receiver loops back to Transmitter    |  |

| Serial Interface Modes      | RS-232 or RS-422/485                  |  |

| I2C Port                    | Bus connected to ADT7420 slave device |  |

| Power Supply Specifications |                                       |  |

| Power Source                | Supplied by user                      |  |

| Input Range                 | 0-55 VDC                              |  |

| Protection                  | 0.55 Amp, 60V resettable fuse         |  |

| General Specifications      |                                       |  |

| Connectors                  | DB-62 male, two 4-pin Molex RA        |  |

| Overvoltage Protection      | -40V to +55V                          |  |

| ESD Protection              | 15 kV                                 |  |

| Power Consumption           | Less than 1 W                         |  |

| Operating Temperature       | -40°C to +85°C                        |  |

| Operating Humidity          | 90%, non-condensing                   |  |

### 201 Test Adapter

The 201 Test Adapter (p/n DNx-TADP-201) is an accessory designed for testing UEI's DNx-AI-201-100 Analog Input Board.

# 3.1 General Description

Under software control, the 201 Test Adapter facilitates DC tests on all 24 single-ended or 12 differential channels of a DNx-Al-201-100 Analog Input Board. The Al-201 is designed to accept differential analog voltage inputs within a  $\pm 15$ V range at sampling rates up to 100kS/s per channel at a resolution of 16 bits.

The 201 Test Adapter receives a ±18VDC reference voltage from the Al-201 and converts it to +2.5V, -2.5V, +5V, and -5V voltages. These voltages are fed back as analog inputs to the AlNn terminals of the Al-201 board.

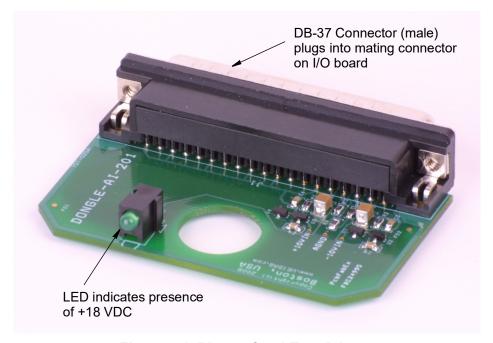

The LED indicates the presence of the +18 VDC output from the Al-201.

Figure 3-1 Photo of 201 Test Adapter

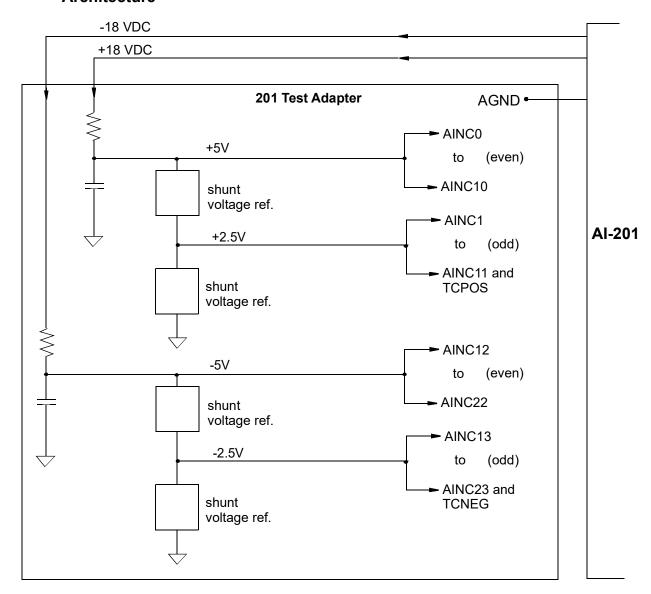

## 3.2 Device Architecture

Figure 3-2 Block Diagram of 201 Test Adapter

As shown in **Figure 3-2** above, the Al-201 outputs two DC voltages (+18V and -18V) to the 201 Test Adapter on terminals 21 and 20, respectively. The +18V is dropped to +5V and distributed to inputs AlNC0, 2, 4, 6, 8, and 10. The -18V is dropped to -5V and distributed to inputs AlNC12, 14, 16,18, and 20. The +5V is dropped to +2.5V and distributed to analog inputs AlNC1, 3, 5, 7, 9, 11 and TCPOS. The -5V is dropped to -2.5V and distributed to inputs AlNC13, 15, 17, 19, 21, 23, and TCNEG.

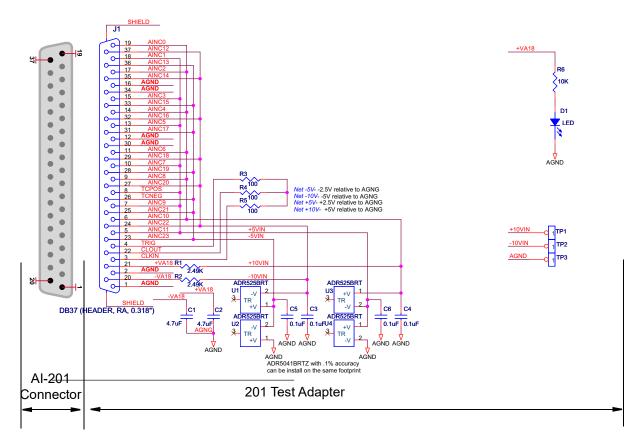

The 201 Test Adapter plugs directly into the DB-37 mating connector of the Al-201. The pinout for the 201 Test Adapter and Al-201 is shown below in **Figure 3-3** alongside the test adapter's schematic.

Figure 3-3 Schematic of 201 Test Adapter

### 3.3 Using the 201 Test Adapter

Testing the DNx-AI-201-100 Analog Input Board with the DNx-TADP-201 requires you to develop a simple program for performing DC tests of each channel and accumulating/displaying the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. Please refer to the DNx-AI-201 User Manual for information about programming the AI-201.

### **3.4 Specifications** Technical specifications for the 201 Test Adapter are listed in **Table 3-1** below.

Table 3-1 Technical Specifications for the DNx-TADP-201

| Channel Configurations      |                                       |  |

|-----------------------------|---------------------------------------|--|

| Number of channels          | 12 differential ( ±15V)               |  |

|                             | 24 single-ended                       |  |

| Input Specifications        |                                       |  |

| Inputs to AI-201            | DC Analog Voltage derived from Al-201 |  |

|                             | ±18VDC                                |  |

| Resolution                  | 16 bits                               |  |

| Power Input to Test Adapter | ±18VDC from AI-201                    |  |

| General Specifications      |                                       |  |

| Connector to AI-201         | DB-37 male                            |  |

| Overvoltage Protection      | -40V to +55V                          |  |

| ESD Protection              | 15 kV                                 |  |

| Power Consumption           | Less than 1 W                         |  |

| Operating Temperature       | -40°C to +85°C                        |  |

| Operating Humidity          | 90%, non-condensing                   |  |

### 201-to-308 Test Adapter

The 201-to-308 Test Adapter (p/n B-D-A-201-308-x and B-D-R-201-308-x) is an accessory designed for combination testing of UEI's DNx-Al-201-100 Analog Input Board and DNx-AO-308 Analog Output Boards of various types. The test adapter requires that the I/O boards be mounted in adjacent slots of a PowerDNA Cube or in adjacent positions of a DNR rack for testing to be performed.

#### 4.1 Features

The key features of the 201-to-308 Test Adapter are:

- Facilitates basic testing of DNx-Al-201-100 Analog Input Board and DNx-AO-308 Analog Output Boards mounted in adjacent slots of a Cube or Rack

- Available in different versions for testing Al-201 in combination with AO-308, AO-308-350, AO-308-353, or AO-308-420

- Simulates analog voltage Inputs to all channels of an Al-201

- LED indicates presence of +15 VDC voltage source from AO-308

- Accepts ±45VDC daisy-chained external power source when configured as 201-308-353 Version

- Provides analog output sensing for 201-308-350 version

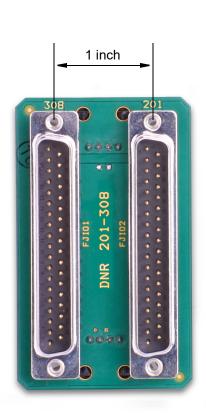

DNR (Rack) Version

DNA (Cube) Version

#### Figure 4-1 Photo of 201-to-308 Test Adapter

# 4.2 General Description

Under software control, the 201-to-308 Test Adapter facilitates tests between DNx-Al-201-100 Analog Input Board and DNx-AO-308 Analog Output Boards. The Al-201-100 is designed to accept 24 single-ended or 12 differential analog voltage inputs within a  $\pm 15 \text{V}$  range at sampling rates up to 100kS/s per channel at a resolution of 16 bits.

The 201-to-308 Test Adapter is offered in several different configurations, depending upon which IO boards are to be tested. First, all versions of the test adapters are offered in either a DNA (Cube) or DNR (Rack) model. Although functionally identical, they differ in the spacing between connectors — the DNA model connectors match the slot spacing of a PowerDNA Cube (0.6 in.); the DNR model connectors match the spacing of modules in a RACKtangle or HalfRACK housing (1.0 in.). The other variations between models relate to the type of AO-308 to be tested.

All versions receive +15VDC and -15VDC power from the AO-308 and +18VDC and -18VDC from the AI-201. The AO-308-353 version also receives ±45VDC power from an external source via a daisy chain cable with resettable fuses in the +VEXT and -VEXT lines. This version is also populated with components required for the ±40VDC output voltage range. An LED indicates the presence of the +V15 voltage.

The version for the basic AO-308 is populated with components with an output range of  $\pm 10$ VDC and is powered from the AO-308. The version for the AO-308-350 is also designed for a high current analog voltage output range of  $\pm 10$ VDC, powered from the AO-308, but which also provides sense lines for more accurate measurement of output voltage on each 308 channel.

The version for the AO-308-353 is populated with components with an output range of ±40VDC and is powered from an external source as noted above.

The version for the AO-308-420 is populated with resistors matched to the higher current ratings of the -420.

The 201 section of the adapter accepts analog voltage inputs from the eight analog outputs of the AO-308 board under test and senses them as analog voltage inputs on the AI-201. It also accepts as analog inputs the +V15, -V15 from the AO-308 board and the +V18, and -V18 from the AI-201 board.

The TRIG-IN, CLKIN, and CLKOUT of the 201 are connected to DIO1, DIO2, and DIO3 of the AO-308.

The LED indicates the presence of the +15 VDC output form the AO-308.

### 4.3 Device Architecture

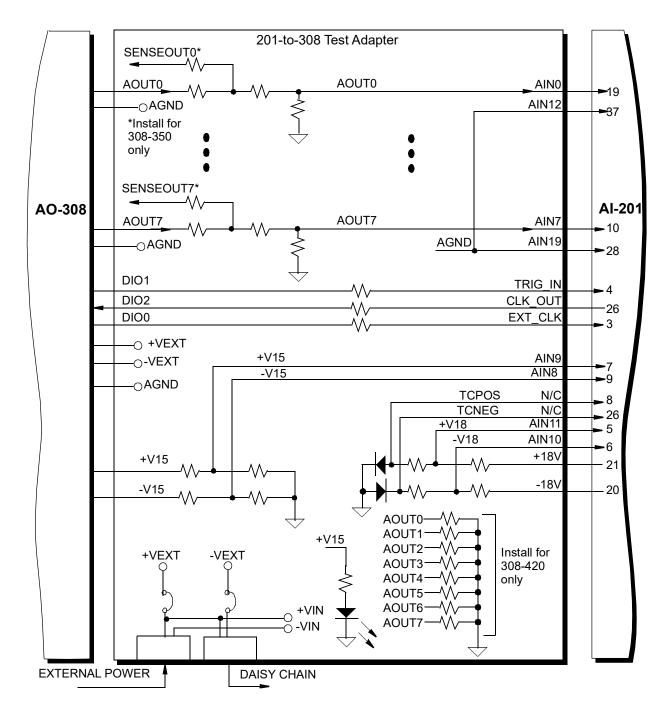

Figure 4-2 Block Diagram of 201-to-308 Test Adapter

As shown in **Figure 4-2** above, an AO-308-350 outputs -10 to +10 VDC analog voltages that are passed to the Al-201 as analog voltage inputs. The 308-350 version of the test adapter feeds back the actual voltage outputs via sense lines for each output.

In all versions of the 201-to-308 Test Adapter, the DIO1 output of the 308 is fed to the 201 as a TRIG input. DIO0 is also used as the Al-201 CLKIN input. The Al-201 CLKOUT signal is passed to the 308 on DIO2.

In the 308-353 version of the test adapter, resistors of values appropriate for a ±40VDC range are used. Connectors are provided on the board to accept a ±45VDC power from an external source and to accommodate a daisy chain to other devices. The external power circuit is protected by resettable fuses.

In the 308-420 version of the test adapter, resistors of values appropriate for the 4-20 mA current input signals are used for generating analog voltage inputs to the Al-201.

In all versions of the test adapter, the +VA18 and -VA18 voltages from the Al-201 are fed back as analog voltage inputs to the Al-201 on AINC10 and AINC11, and lower values to TCPOS and TCNEG. The +V15 and -V15 voltages from the AO-308 are input to the Al-201 as AINC9 and AINC8.

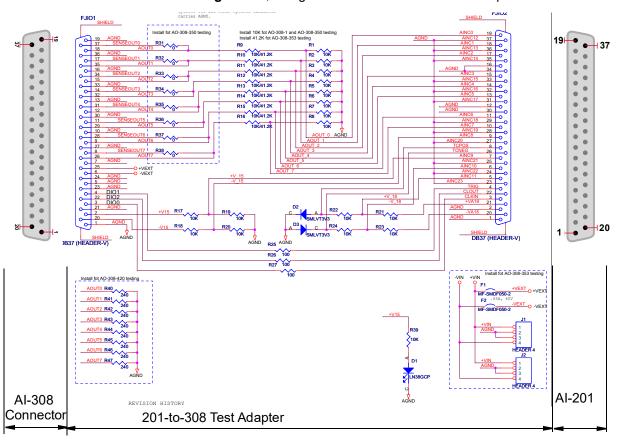

The pinouts of the AO-308, the AI-201, and the 201-to-308 Test Adapter are shown in **Figure 4-3**, along with a schematic of the test adapter circuit.

Figure 4-3 Schematic of 201-to-308 Test Adapter

4.4 to-308 Test **Adapter**

Using the 201- Testing the DNx-AI-201-100 Analog Input Board and DNx-AO-308 Analog Output Boards with the 201-to-308 Test Adapter requires you to develop a simple program for performing tests of each channel and accumulating/ displaying the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. In particular, UEI Framework contains examples in the Analog Input folders and Analog Output folders that can be used to operate the AI-201 and AO-308 boards together. Please refer to the DNx-Al-201 and AO-308 User Manuals for information about programming the AI-201 and AO-308.

### 4.5

Specifications Technical specifications for the 201-to-308 Test Adapter are listed in Table 4-1 below.

Table 4-1 Technical Specifications

| Channel Configurations      |                                             |  |

|-----------------------------|---------------------------------------------|--|

| No.of channels              | 8 in, 12 out                                |  |

| Isolation                   | 350 Vrms (chan-to-chan and chan-to-chassis) |  |

| Input/Output Specifications |                                             |  |

| Inputs                      | 8 analog voltage from AO-308, 3 DIO from    |  |

|                             | AO-308 and AI-201                           |  |

| Outputs                     | 8 analog voltage sense (±10 VDC) for 308-   |  |

|                             | 350, Two ±18VDC, Two ±15VDC                 |  |

| Resolution                  | 16 bits                                     |  |

| Power Input                 | +45VDC from external source for AO-308-353  |  |

|                             | only, (daisy-chained)                       |  |

| Power Output                | +V15, -V15 to AI-201                        |  |

| General Specifications      |                                             |  |

| Connector                   | Two DB-37 male                              |  |

| Overvoltage                 | -40V to +55V                                |  |

| protection                  |                                             |  |

| ESD Protection              | 2000 V ESD                                  |  |

| Power                       | Less than 1 W                               |  |

| Consumption                 |                                             |  |

| Operating                   | -40°C to +85°C                              |  |

| Temperature                 |                                             |  |

| Operating                   | 0 to 95%, non-condensing                    |  |

| Humidity                    |                                             |  |

### 202 Test Adapter

The 202 Test Adapter (p/n DNx-TADP-202) is an accessory designed for testing UEI's DNx-AI-202 Analog Current Input Board.

# 5.1 General Description

Under software control, the 202 Test Adapter facilitates tests on all 12 differential input channels of a DNx-Al-202 Analog Current Input Board. The Al-202 is designed to accept differential analog current inputs within any of three ranges (±1.5mA, ±15mA, or ±150mA) at sampling rates up to 16 kS/s aggregate.

The 202 Test Adapter receives a +18V reference voltage from the Al-202 and converts it to a +10VDC voltage, which drives a current through the resistors connected across the terminals of the differential inputs of the Al-202 board. The current through the resistors, which are all connected in series by the test adapter, produces voltage drops that, in turn, are measured as analog voltage inputs to the Al-202. An opto-relay in the test adapter switches resistance values to give two current values through the input shunt resistors.

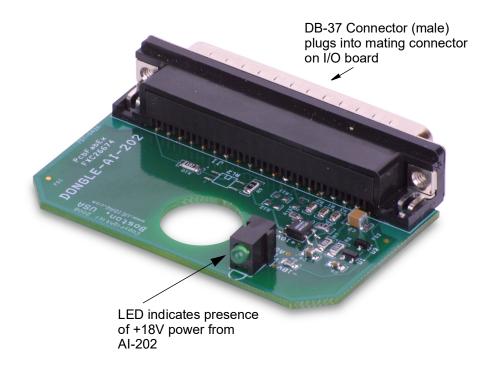

Figure 5-1 Photo of 202 Test Adapter

## 5.2 Device Architecture

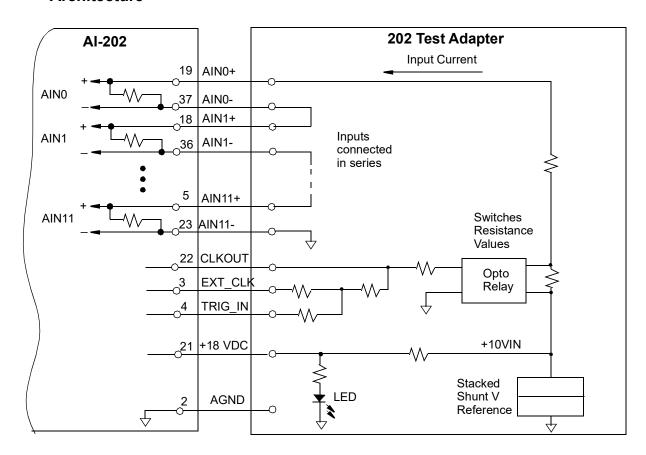

Figure 5-2 Block Diagram of 202 Test Adapter

As shown in **Figure 5-2** above, the Al-202 outputs a DC voltage (+18V) to the Test Adapter. This voltage is regulated by a shunt voltage reference to +10VDC (+VIN), which is then fed through all Al-202 input shunt resistors in series to ground. The voltage drops through the series of input shunt resistors produce voltages on each that are sensed as input signals for the Al-202. These measured values are then compared to known reference values for testing performance of the Al-202.

An opto-relay changes the value of a resistor in the series circuit for all of the Al-202 input shunt resistors, thus making it possible to sense all inputs at two different values of current.

A circuit is also included for testing the TC POS and NEG leads, a feature not currently implemented in the Al-202.

An LED on the Test Adapter indicates presence of the +18V supplied by the Al-202.

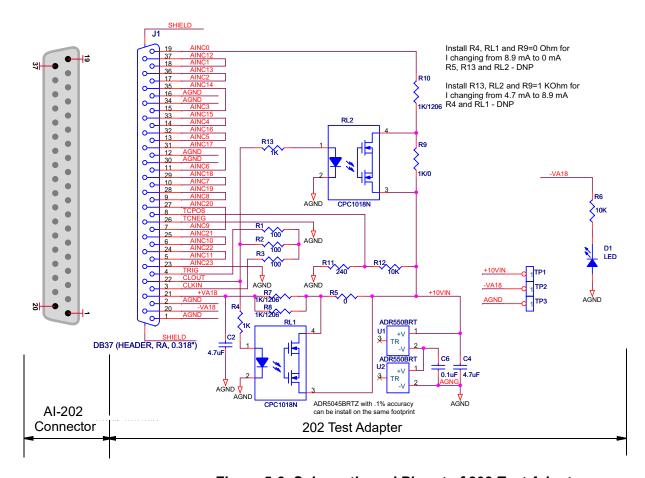

The pinouts of the Al-202 and the 202 Test Adapter are shown in **Figure 5-3**, along with a schematic of the Test Adapter circuit.

Figure 5-3 Schematic and Pinout of 202 Test Adapter

# 5.3 Using the 202 Test Adapter

Testing the DNx-Al-202 Analog Current Input Board with the DNx-TADP-202 requires you to develop a simple program for performing tests of each channel and accumulating/displaying the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. Please refer to the DNx-Al-202 User Manual for information about programming the Al-202.

### **5.4 Specifications** Technical specifications for the 202 Test Adapter are listed in **Table 5-1** below.

Table 5-1 Technical Specifications for the 202 Test Adapter

| Channel Configurations      |                                          |  |

|-----------------------------|------------------------------------------|--|

| Number of channels          | 12 differential current inputs to Al-202 |  |

| Input Ranges to AI-202      | ±1.5mA, ±15mA, ±150mA                    |  |

| Shunt Resistance            | 10-ohm, 0.1%                             |  |

| (across AI-202 Inputs)      |                                          |  |

| Isolation                   | 1500 Vrms                                |  |

| Power Input to Test Adapter | +18VDC from Al-202                       |  |

| General Specifications      |                                          |  |

| Connector                   | DB-37 male                               |  |

| Overvoltage protection      | -40V                                     |  |

| ESD Protection              | 2000V                                    |  |

| Power Consumption           | Less than 1 W                            |  |

| Operating Temperature       | -40°C to +85°C                           |  |

| Operating Humidity          | 95%, non-condensing                      |  |

### 205 Test Adapter

The 205 Test Adapter (p/n DNx-TADP-205) is an accessory designed for testing UEI's DNx-AI-205 Analog Input Board.

### 6.1 General Description

Under software control, the 205 Test Adapter facilitates tests on all four differential input channels and all eight bidirectional DIO channels of a DNx-Al-205 Board. The Al-205 is designed to accept differential analog voltage inputs within a maximum range of ±100V at sampling rates up to 250 kHz per channel (500 kS/s aggregate). An individual ADC with 18-bit resolution and simultaneous sampling is provided for each channel. Each of the four analog input channels also has two DIOs per channel.

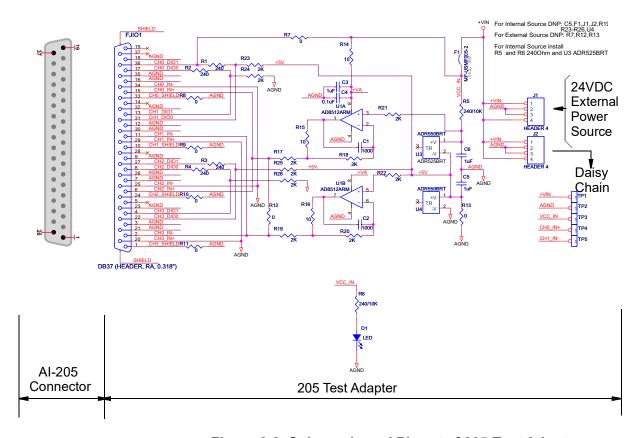

## 6.2 Device Architecture

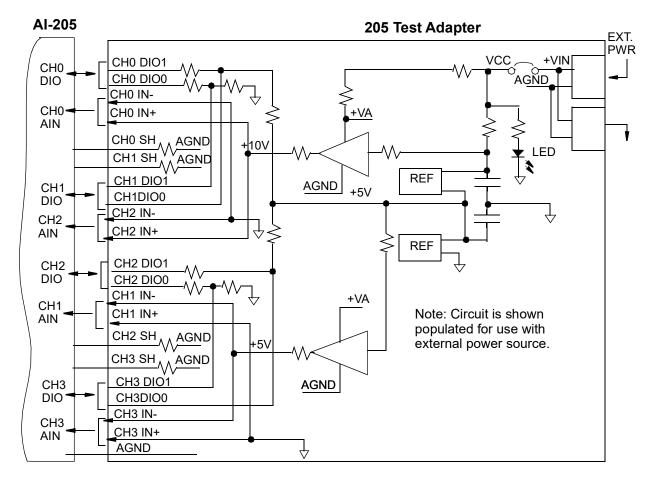

Figure 6-1 Block Diagram of 205 Test Adapter

As shown in the simplified circuit diagram of **Figure 6-1** above, the 205 Test Adapter receives power from an external source, which is daisy-chained to/from other devices. An on-board LED indicates presence of the external power voltage. The 24VDC external power circuit is protected by a resettable fuse.

As shown in the diagram, the incoming power voltage is regulated down to +5V for input to two analog voltage inputs (CH1 and CH3) on the Al-205 and to +10V for the two others (CH0 and CH1).

The +5V and AGND are also used for the DIO channels on the AI-205. Since the DIO channels are bidirectional and cross-connected (Ch 0 and Ch1, Ch 2 and Ch3), the test program can be designed to simulate digital inputs and outputs on all four channels in either direction.

The pinouts of the Al-205 and the 205 Test Adapter are shown in **Figure 6-2**, along with a schematic of the Test Adapter circuit.

Figure 6-2 Schematic and Pinout of 205 Test Adapter

### 6.3 Using the 205 Test Adapter

Testing the DNx-Al-205 Analog Input Board with the DNx-TADP-205 requires you to develop a simple program for performing tests of each channel and accumulating/displaying the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. Please refer to the DNx-Al-205 User Manual for information about programming the Al-205.

**6.4 Specifications** Technical specifications for the 205 Test Adapter are listed in **Table 6-1** below.

Table 6-1 Technical Specifications for the 205 Test Adapter

| Channel Configurations      |                                         |

|-----------------------------|-----------------------------------------|

| Number of channels          | 4 differential voltage inputs to Al-205 |

| Input Impedance             | 2 Mohm (to ground), 4 Mohm              |

|                             | (differential)                          |

| Input Ranges to AI-205      | ±100V, ±10V, ±1V, ±0.1V                 |

| Power Input to Test Adapter | +24VDC from external source             |

| General Specifications      |                                         |

| Connector                   | DB-37 male                              |

| Overvoltage protection      | ±150V (powered or unpowered)            |

| ESD Protection              | 2000V                                   |

| Power Consumption           | Less than 1 W.                          |

| Operating Temperature       | -40°C to +85°C                          |

| Operating Humidity          | 0 to 95%, non-condensing                |

### 207/217 Test Adapter

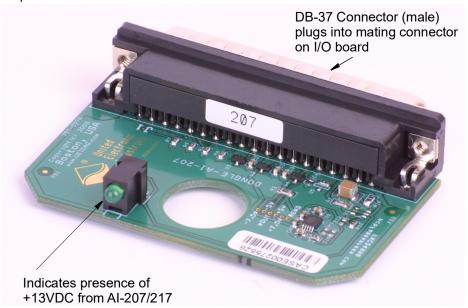

The 207/217 Test Adapter (p/n DNx-TADP-207-17) is an accessory designed for testing UEI's DNx-AI-207 and DNx-AI-217 Analog Input Boards.

# 7.1 General Description

Under software control, the 207/217 Test Adapter facilitates tests on all 17 channels (16 analog voltage differential inputs plus one single ended CJC voltage) of a DNx-Al-207 or DNx-Al-217 Analog Input Board.

The 207/217 Test Adapter receives a +13V reference voltage from the Al-207/217 and converts it to +7.5V, +5V, and -2.5V voltages, which are looped back as analog inputs to the I/O board. The voltages are connected as follows:

- 7.5VDC to inputs AIN0+, AIN2+, AIN4+, AIN6+, AIN8+, AIN10+, AIN12+, and AIN14+

- 5VDC to AIN1-, AIN3-, AIN5-, AIN7-, AIN9-, AIN11-, AIN13-, AIN15-

- -2.5VDC to AIN1+, AIN3+, AIN5+, AIN7+, AIN9+, AIN11+, AIN13+, AIN15+

- 0VDC (GND) to AIN0-, AIN2-, AIN4-, AIN6-, AIN8-, AIN10-, AIN12-, and AIN14-

- The XTRIG signal from the Al-207/217 switch U1, if installed, turns the +13V power on and off.

Figure 7-1 Photo of 207/217 Test Adapter

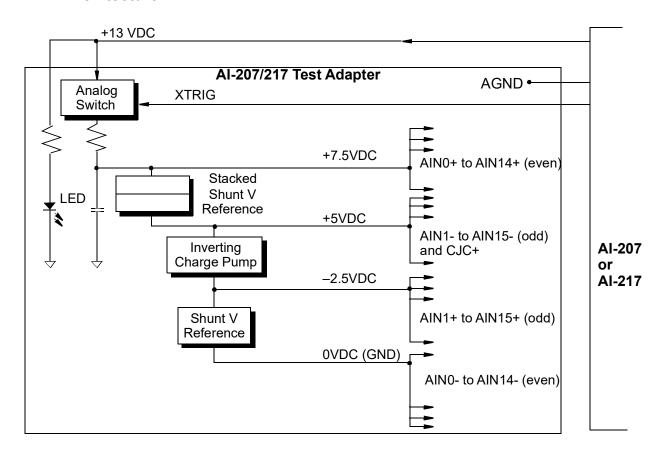

# 7.2 Device Architecture

Figure 7-2 Block Diagram of 207/217 Test Adapter

As shown in **Figure 7-2** above, the Al-207/217 outputs a 13VDC voltage to the Test Adapter. This voltage is fed through an analog switch controlled via a trigger from the Al-207/217. The current through the switch passes through a resistor and two shunt voltage references to ground, which drops the voltage to 7.5V and +5 VDC. The +5 V is then passed to an inverting charge pump that outputs -10 VDC. The -10 V is fed through a shunt voltage reference to produce a -2.5 V signal. These three reference voltages and GND are connected as inputs to the terminals of the Al-207/217 Analog Input Board.

Differential measurements should therefore result in +7.5V on even channels and -7.5V on odd channels. On the Al-207, the CJC buffer will produce an expected CJC reading of +2.5V. The CJC channel is not recommended for use on the Al-217.

The pinouts of the Al-207/217 and the 207/217 Test Adapter are shown in **Figure 7-3**, along with a schematic of the Test Adapter circuit.

Figure 7-3 Schematic of 207/217 Test Adapter

#### 7.3 **217 Test Adapter**

Using the 207/ Testing the DNx-Al-207 and DNx-Al-217 Analog Input Boards with the DNx-TADP-207-17 requires you to develop a simple program for performing tests of each channel and accumulating/displaying the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. Please refer to the DNx-Al-207/217 User Manual for information about programming the AI-207/217.

### 7.4

**Specifications** Technical specifications for the 207/217 Test Adapter are listed in **Table 7-1** below.

Table 7-1 Technical Specifications for the 207/217 Test Adapter

| Channel Configurations      |                                           |

|-----------------------------|-------------------------------------------|

| Number of channels          | 16 differential (8 at +7.5V, 8 at -7.5V), |

|                             | 1 single-ended CJC channel                |

| Programmable DIO line       | One (external trigger) for switching +13V |

|                             | on and off. Controlled from Al-207/217.   |

| Input Specifications        |                                           |

| Inputs to AI-207/217        | DC Analog Voltage                         |

|                             | (+7.5V, -2.5V, +5V, 0V)                   |

| Power Input to Test Adapter | +13VDC from AI-207/217                    |

| General Specifications      |                                           |

| Connector                   | DB-37 male                                |

| Overvoltage protection      | -40V to +55V                              |

| ESD Protection              | 15 kV                                     |

| Power Consumption           | Less than 1 W                             |

| Operating Temperature       | -40°C to +85°C                            |

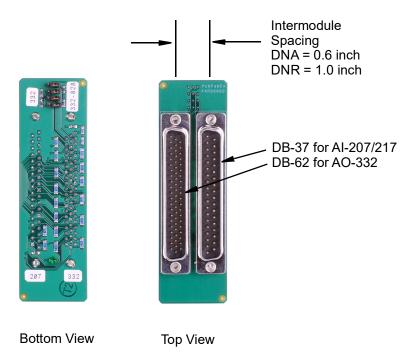

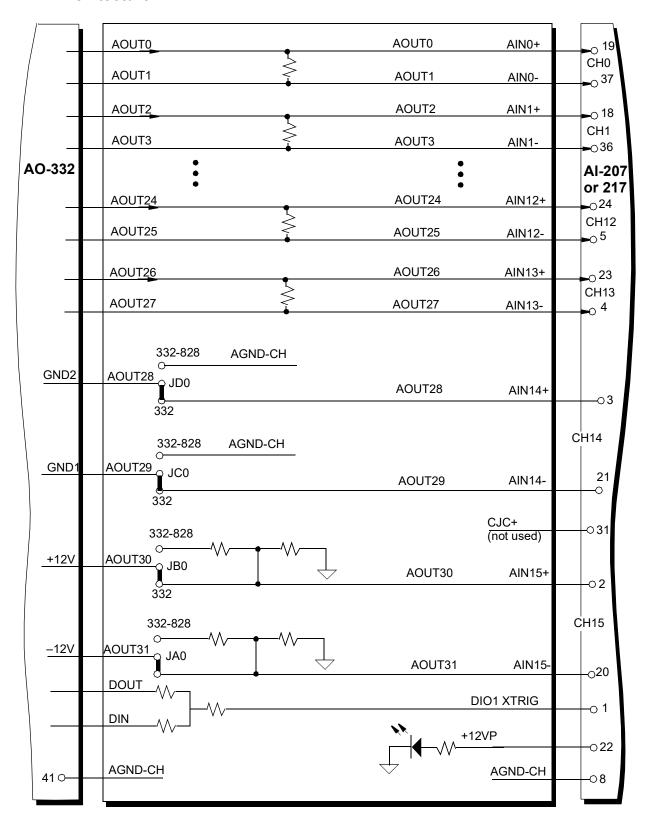

### 207-to-332 Test Adapter

The 207-to-332 Test Adapter (p/n B-D-DNA-207-332 and B-D-DNR-207-332) is an accessory designed for combination testing of UEI's DNx-AI-207/217 Analog Input Board and DNx-AO-332 Analog Output Board. The test adapter requires that the I/O boards be mounted in adjacent slots of a PowerDNA Cube or in adjacent positions of a DNR rack for testing to be performed.

#### 8.1 Features

The key features of the 207-to-332 Test Adapter are:

- Facilitates basic testing of DNx-Al-207/217 Analog Input Board and DNx-AO-332 Analog Output Board mounted in adjacent slots of a Cube or Rack

- On-board jumper selector permits testing AI-207 or AI-217 in combination with either AO-332 or AO-332-828

- AO-332 simulates analog voltage inputs to all channels of an AI-207217

I/O Board

- LED indicates presence of +12 VDC voltage source from AI-207/217

Figure 8-1 Photo of 207-to-332 Test Adapter

# 8.2 General Description

Under software control, the 207-to-332 Test Adapter facilitates tests on all 16 differential input channels of a DNx-Al-207 or DNx-Al-217 Analog Input Board or all 32 channels of the AO-332 Analog Output Board. Since the Al-207/217 accepts only 16 differential analog voltages, the Test Adapter combines pairs of single-ended analog outputs of the AO-332 into 16 differential voltage inputs to the Al-207/217.

The 207-to-332 Test Adapter is offered in two different versions, depending upon which I/O boards are to be tested. The Test Adapter is offered in either a DNA (Cube) or DNR (Rack) model. Although functionally identical, they differ in the spacing between connectors — the DNA model connectors match the slot spacing of a PowerDNA Cube; the DNR model connectors match the spacing of modules in a RACKtangle or HalfRACK housing. Both versions have an-board jumper selector that permits testing of either a standard AO-332 or an AO-332-828.

The Al-207/217 also has a bidirectional DIO line connected through resistors with DIN and DOUT lines on the AO-332.

When the Test Adapter jumpers are set to test a standard AO-332, the jumpers are placed into the 1-2 position. This connects AOUT28 and AOUT29 directly to inputs AIN14+ and AIN14- on the AI-207/217, (Analog Input Channel 14). In this mode, AOUT30 and AOUT31 output a constant +12V and -12V, respectively. These voltages are connected directly to inputs AIN15+ and AIN15- (AI-207/217 input Channel 15).

When the Test Adapter jumpers are set to the AO-332-828 position (position 2-3), AOUT 27 and AOUT28 are connected to AGND-CH. In this mode, AOUT30 and AOUT31, which carry +12V and 12V from the 332, are connected through a voltage divider circuit (which drops the voltage to about 8V) to AIN15+ and AIN15- (Channel 15) on the AI-207/217.

An LED indicates the presence of the +12 VDC output form the AI-207/217.

#### AO-333 Compatibility

While you can use the 207-to-332 Test Adapter with the AO-333, it is more convenient to test the AO-333 directly using its Guardian Readback feature.

## 8.3 Device Architecture

Figure 8-2 Block Diagram of 207-to-332 Test Adapter

DNP FOR AO-332 RE0 21K 10K RG0 AIN16 37 AIN1 18 AIN17 36 **√**21K • . JB0 JCÔ J1 - J4 1-2 AO-332 J1 - J4 2-3 AO-332-828 AIN2 0 20 R0 <a>10K</a> AOUT11 D0 AOUT10 AOUT12 AOUT13 LN38GCP 10K AOUT18 AOUT19 AOUT21 AOUT25 AOUT27 AOUT29 AOUT30 AOUT31 AI-207 AI-332 or 217 Connector 207-332 Test Adapter

The pinouts of the AO-332, the AI-207/217, and the 207-to-332 Test Adapter are shown in Figure 8-3, along with a schematic of the test adapter circuit.

Figure 8-3 Schematic and Pinout of 207-to-332 Test Adapter

#### 8.4 to-332 Test **Adapter**

Using the 207- Testing the DNx-AI-207/217 Analog Input Board and DNx-AO-332 Analog Output Board with the 207-to-332 Test Adapter requires you to develop a simple program for performing tests of each channel and accumulating/displaying the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. In particular, UEI Framework contains examples in the Analog Input folders and Analog Output folders that can be used to operate the AI-207 and AO-332 boards together. Please refer to the DNx-Al-207, DNx-Al-217, and/or DNx-AO-332 User Manuals for information about programming the I/O boards.

#### 8.5

Specifications Technical specifications for the 207-to-332 Test Adapter are listed in Table 8-1 below.

Table 8-1 Technical Specifications

| Channel Configura  | Channel Configurations                      |  |

|--------------------|---------------------------------------------|--|

| No.of channels     | 32 analog inputs, 16 analog outputs, 1 DIO  |  |

| Channel            | AO-332 even channel <-> AI-207 +channel     |  |

| configurations     | AO-332 odd channel <-> AI-207 -channel      |  |

|                    | (e.g., AOut0 <-> AIN0+ and AOut1 <-> AIN0-) |  |

|                    | AO-332 DIO <-> AI-207/217 XTrig             |  |

| General Specificat | ions                                        |  |

| Connector          | One DB-37 male to AI-207/217                |  |

|                    | One DB-62 male to AO-332                    |  |

| Overvoltage        | -40V to +55V                                |  |

| protection         |                                             |  |

| ESD Protection     | 2000 V ESD                                  |  |

| Power              | 3W (AO-332)                                 |  |

| Consumption        |                                             |  |

| Operating          | -40°C to +85°C                              |  |

| Temperature        |                                             |  |

| Operating          | 0 to 95%, non-condensing                    |  |

| Humidity           |                                             |  |

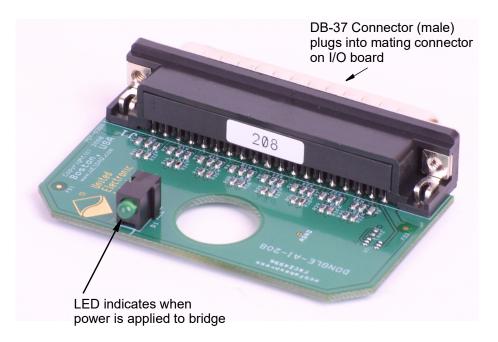

### 208 Test Adapter

The 208 Test Adapter (p/n DNx-TADP-208) is an accessory designed for testing UEI's DNx-AI-208 Strain/Bridge Analog Input Board.

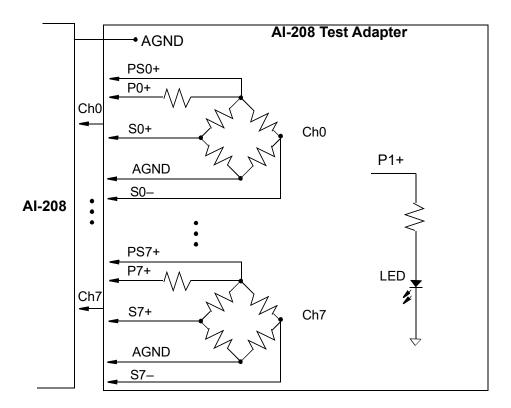

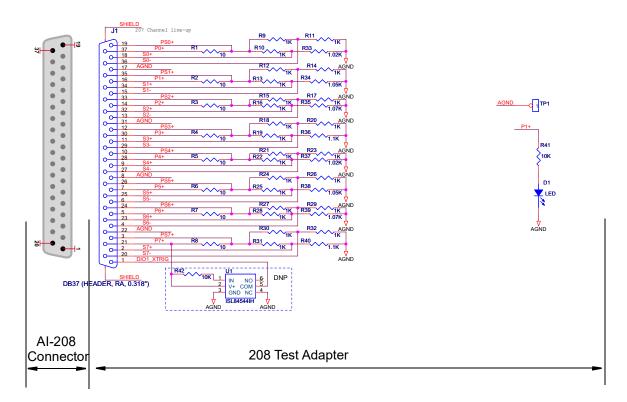

# 9.1 General Description

Under software control, the 208 Test Adapter facilitates tests on all 8 channels of a DNx-AI-208 Analog Input Board. The AI-208 is designed to accept analog voltage inputs from full, half, and quarter-bridge strain gauges. The 208 Test Adapter connects a full Wheatstone bridge to each of the eight input channels of the AI-208.

Figure 9-1 Photo of 208 Test Adapter

# 9.2 Device Architecture

As shown in **Figure 9-2**, the 208 Test Adapter connects a fixed-resistor bridge circuit to each Al-208 channel. Channel 0 and 4 have a 2% unbalance, Ch1 and Ch5 have 5%, Ch2 and Ch6 have 7%, Ch3 and Ch7 have 10%.

The LED is ON when P1+ is present to indicate that power is applied to the bridge.

The XTRIG signal is not currently used.

Figure 9-2 Block Diagram of 208 Test Adapter

The pinouts of the Al-208 and the 208 Test Adapter are shown in **Figure 9-3**, along with a schematic of the Test Adapter circuit.

Figure 9-3 Schematic and Pinout of 208 Test Adapter

# 9.3 Using the 208 Test Adapter

Testing the DNx-AI-208 Strain/Bridge Analog Input Board with the DNx-TADP-208 requires you to develop a simple program for performing tests of each channel and accumulating/displaying the test results. This can be done by using the sample code provided by UEI as guides and modifying them to fit your specific needs. The code samples are included in the UEI software suite. Please refer to the DNx-AI-208 User Manual for information about programming the AI-208.

### **9.4 Specifications** Technical specifications for the 208 Test Adapter are listed in **Table 9-1** below.

Table 9-1 Technical Specifications for the 208 Test Adapter

| Channel Configurations |                                           |

|------------------------|-------------------------------------------|

| Number of channels     | 8 full-bridge strain gauge inputs         |

| Indicating LED         | One LED indicates Power On when           |

|                        | voltage is aplied to Ch 1 bridge.         |

| Input Specifications   |                                           |

| Inputs to AI-208       | Fixed-resistor Wheatstone bridge with     |

|                        | one resistor specified to give a specific |

|                        | unbalance.                                |

| General Specifications |                                           |

| Connector              | DB-37 male                                |

| Overvoltage protection | -40V to +55V                              |

| ESD Protection         | 15 kV                                     |

| Power Consumption      | Less than 1 W                             |

| Operating Temperature  | -40°C to +85°C                            |

### 211 Test Adapter

The 211 Test Adapter (p/n DNx-TADP-211) is an accessory designed for testing UEI's DNx-AI-211 Vibration Interface Board.

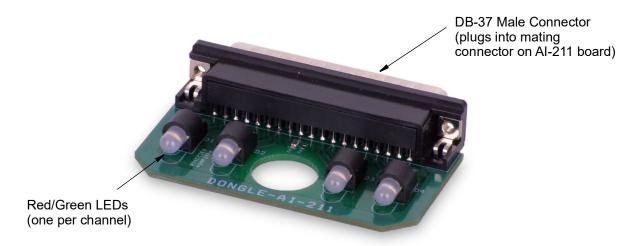

#### 10.1 Features

The key features of the 211 Test Adapter are:

- Facilitates basic DC testing of DNx-AI-211 Boards

- Performs loopback tests to verify operation of DC bias current output through 3.6K resistor using analog input voltage

- · Allows testing of open circuit and short circuit trip points

- 4 Independent channels with 2-color (Red/Green) indicating LEDs on each for visual verification of bias current operating point

- Allows testing of AC and DC coupling

# 10.2 General Description

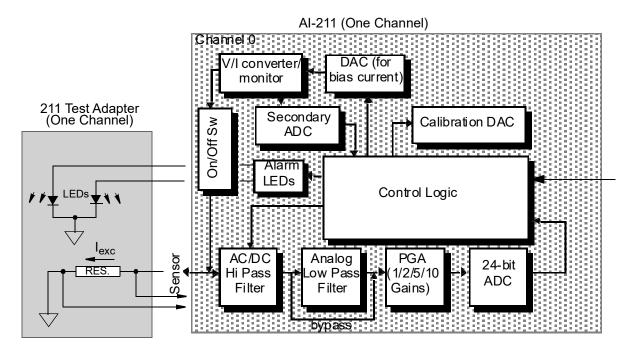

Under software control, the 211 Test Adapter facilitates loopback tests on all four channels of a DNx-Al-211 IEPE/ICP Vibration Sensor Interface Board. The Al-211, which is designed to interface directly with industry standard IEPE/ICP vibration sensors, outputs a DAC-controlled 0-8 mA DC current on each of four channels. This current is typically used to bias an IEPE/ICP vibration sensor, one per channel. The output of a sensor is an AC signal superimposed on a DC voltage. Vibration measurements look only at the AC component and usually use AC coupling to remove the DC component. The AC component is then filtered, amplified, and fed to a 24-bit ADC.

For this test, however, no AC component is present. The 211 Test Adapter, therefore, tests operation and accuracy of the bias current circuit (DAC, V/I converter/monitor, Secondary ADC, PGA, and 24-bit ADC on each of the four channels. It does not, however, test AC performance of AI-211 or the vibration sensor itself.

Figure 10-1 Photo of 211 Test Adapter

#### 10.3 Device Architecture