# DNA-PPCx-1G & UEINet PowerDNA® Gigabit Ethernet I/O Cube User Manual

October 2018 PN Man-DNA-PPCx-1G Information furnished in this manual is believed to be accurate and reliable. However, no responsibility is assumed for its use, or for any infringement of patents or other rights of third parties that may result from its use.

All product names listed are trademarks or trade names of their respective companies.

See the UEI website for complete terms and conditions of sale:

http://www.ueidaq.com/cms/terms-and-conditions/

### **Contacting United Electronic Industries**

### **Mailing Address:**

27 Renmar Avenue Walpole, MA 02081 U.S.A.

For a list of our distributors and partners in the US and around the world, please contact a member of our support team:

### Support:

Telephone: (508) 921-4600 Fax: (508) 668-2350

Also see the FAQs and online "Live Help" feature on our web site.

### **Internet Support:**

Support: <a href="mailto:support@ueidaq.com">support@ueidaq.com</a>

Website: <a href="mailto:support@ueidaq.com">www.ueidaq.com</a>

FTP site: <a href="mailto:ftp://ftp.ueidaq.com">ftp://ftp.ueidaq.com</a>

### **Product Disclaimer:**

#### **WARNING!**

### DO NOT USE PRODUCTS SOLD BY UNITED ELECTRONIC INDUSTRIES, INC. AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

Products sold by United Electronic Industries, Inc. are not authorized for use as critical components in life support devices or systems. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Any attempt to purchase any United Electronic Industries, Inc. product for that purpose is null and void and United Electronic Industries Inc. accepts no liability whatsoever in contract, tort, or otherwise whether or not resulting from our or our employees' negligence or failure to detect an improper purchase.

Specifications in this document are subject to change without notice. Check with UEI for current status.

### **Table of Contents**

| Chapter                        | 1 Introduction                                                                                                                                     |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                            | Organization of This Manual                                                                                                                        |

| 1.2                            | Manual Conventions                                                                                                                                 |

| 1.3                            | Product Versions.                                                                                                                                  |

| Chapter                        | 2 The PowerDNA DNA-PPCx-1G Cube System Description                                                                                                 |

| 2.1                            | PowerDNA Gigabit Ethernet Cube Overview                                                                                                            |

| 2.2                            | Specifications                                                                                                                                     |

| 2.3                            | Key Features                                                                                                                                       |

| 2.4<br>2.4.1                   | PowerDNA DNA-PPCx-1G Cube Enclosure                                                                                                                |

| 2.5                            | Front Panel Ports, Connections & LEDs                                                                                                              |

| 2.6<br>2.6.1<br>2.6.2          | PowerDNA CPU/POWER Core Module                                                                                                                     |

| 2.7                            | PowerDNA I/O Boards                                                                                                                                |

| Chapter                        | 3 Installation and Configuration 1                                                                                                                 |

| 3.1<br>3.1.1<br>3.1.2          | Initial Installation Guide       1         Inspect Package       1         Install Software       1                                                |

| 3.2                            | Initial Boot-up                                                                                                                                    |

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3 | IP Address Overview & Update Procedures                                                                                                            |

| 3.4<br>3.4.1                   | Network Configuration                                                                                                                              |

| 3.5<br>3.5.1<br>3.5.2          | Troubleshooting       2         Troubleshooting System Communication       2         Troubleshooting Communication after Reset       3             |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3 | Updating Firmware3Determining Currently Installed Firmware Version3Updating Firmware via PowerDNA Explorer3Updating Firmware via Serial Interface3 |

| 3.7<br>3.7.1<br>3.7.2<br>3.7.3 | Mounting and Field Connections3Physical Dimensions3Pinout Diagrams3Network Wiring3                                                                 |

| 3.8                            | Wiring I/O Boards                                                                                                                                  |

| 3.9                            | Repairing / Upgrading a Cube System                                                                                                                |

| 3.10<br>3.10.1                 | Configuring a NIC Port for Diagnostic Mode                                                                                                         |

| 3.10.2<br>3.10.3                                                                                         | Reading Configuration and Status in Diagnostic Mode                                                                                                                                                                                                                                                                                                     |                                              |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.11<br>3.11.1<br>3.11.2                                                                                 | Disabling Writes to Flash/EEPROM (NVRAM)                                                                                                                                                                                                                                                                                                                | 46                                           |

| Chapter                                                                                                  | 4 PowerDNA Explorer                                                                                                                                                                                                                                                                                                                                     | 48                                           |

| 4.1                                                                                                      | Getting Started with PowerDNA Explorer                                                                                                                                                                                                                                                                                                                  | 48                                           |

| 4.2                                                                                                      | Connecting PowerDNA Explorer to Your System                                                                                                                                                                                                                                                                                                             | 49                                           |

| 4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                  | Overview of the Main Window  Menu Bar  Toolbar  Device Tree  Settings Panel                                                                                                                                                                                                                                                                             | 51<br>56<br>57                               |

| 4.4                                                                                                      | Example of Digital Input/Output Board Settings                                                                                                                                                                                                                                                                                                          | 31                                           |

| 4.5                                                                                                      | Example of Analog Output Board Settings                                                                                                                                                                                                                                                                                                                 | 64                                           |

| 4.6                                                                                                      | Example of Analog Input Board Settings                                                                                                                                                                                                                                                                                                                  | 65                                           |

| 4.7                                                                                                      | Example of Counter/Timer Board Settings                                                                                                                                                                                                                                                                                                                 | 66                                           |

| Chapter                                                                                                  | 5 Programming CPU Board-specific Parameters                                                                                                                                                                                                                                                                                                             | 69                                           |

| 5.1                                                                                                      | Overview                                                                                                                                                                                                                                                                                                                                                | 69                                           |

| 5.2                                                                                                      | Memory Maps                                                                                                                                                                                                                                                                                                                                             | 69                                           |

| 5.3                                                                                                      | Startup Sequence                                                                                                                                                                                                                                                                                                                                        | 71                                           |

| 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.4.9<br>5.4.10<br>5.4.11 | Setting and Reading CPU Core Parameters via Serial Port Help Command Show System Parameters Command Set and Store Commands Set and Store Example Reset Command Password Command Display I/O Board Table Command Display Power Diagnostics Command Memory Test/Memory Clear Command Monitor CPU and Pbuf Usage Command Clock and Watchdog Access Command | 72<br>73<br>74<br>75<br>76<br>77<br>79<br>79 |

| Append                                                                                                   | ix A 8                                                                                                                                                                                                                                                                                                                                                  | 81                                           |

| Network                                                                                                  | Interface Card Configuration                                                                                                                                                                                                                                                                                                                            |                                              |

| A.1 (                                                                                                    | Configuring an Ethernet Card on Windows 7                                                                                                                                                                                                                                                                                                               | 31                                           |

| Append                                                                                                   | ix B {                                                                                                                                                                                                                                                                                                                                                  | 85                                           |

| Field Re                                                                                                 | placement of Fuses on DNA Boards                                                                                                                                                                                                                                                                                                                        |                                              |

| Index                                                                                                    |                                                                                                                                                                                                                                                                                                                                                         | 87                                           |

### **List of Figures**

| Chapte       | r 1 Introduction                                                            | 1    |

|--------------|-----------------------------------------------------------------------------|------|

| Chapte       | r 2 The PowerDNA DNA-PPCx-1G Cube System Description                        | 4    |

| 2-1          | UEI PowerDNA DNA-PPC9-1G & UEINet Systems                                   |      |

| 2-2          | Technical Specifications                                                    |      |

| 2-3          | Product Features                                                            | 7    |

| 2-4          | Air Flow through PowerDNA Cube                                              | 8    |

| 2-5          | PowerDNA 1G Cube Front Panel Arrangement                                    | 9    |

| 2-6          | DNA-PPCx-1G Front Panel LEDs                                                |      |

| 2-7          | Functional Block Diagram of DNA-PPCx-1G Core Module (2 Boards)              | 11   |

| Chapte       | r 3 Installation and Configuration                                          | . 16 |

| 3-1          | Typical MTTTY Screen after DNA-PPCx-1G Boot-up                              |      |

| 3-2          | Using PowerDNA Explorer to Change IP Address                                |      |

| 3-3          | Single DNA-PPCx-1G Direct-Connected to Host without LAN Switch              |      |

| 3-4          | Single Network for Operation and Diagnostics Using Cubes and One LAN Switch |      |

| 3-5          | Separate Networks for Operation and Diagnostics:                            |      |

| Two Cu       | bes & Two Switches25                                                        |      |

| 3-6          | Typical Configuration for a Single DNA-PPCx-1G with a LAN Switch            | 28   |

| 3-7          | Show Interfaces                                                             | 30   |

| 3-8          | Show Interface Parameters                                                   |      |

| 3-9          | Displaying the Version of Your Firmware                                     |      |

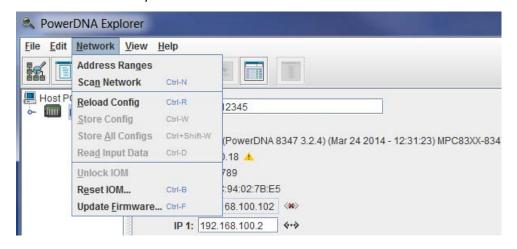

| 3-10         | Update Firmware Menu Item                                                   |      |

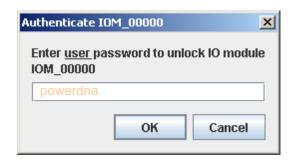

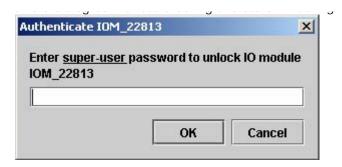

| 3-11         | Password Dialog Box                                                         |      |

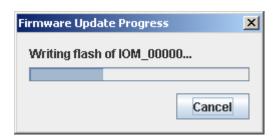

| 3-12         | Firmware Update Progress Dialog Box                                         |      |

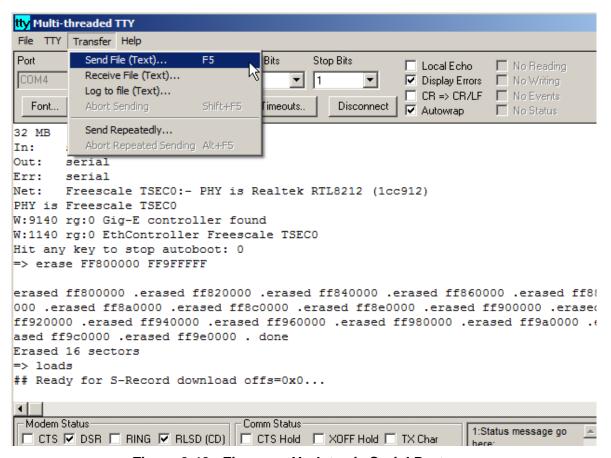

| 3-13         | Firmware Update via Serial Port                                             |      |

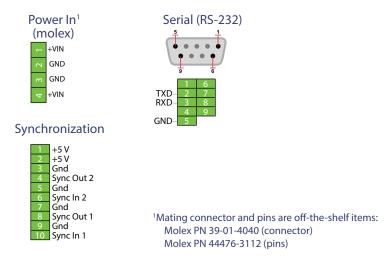

| 3-14         | DNA-PPCx-1G Pinout Diagrams                                                 |      |

| 3-15         | Example of System Configuration                                             |      |

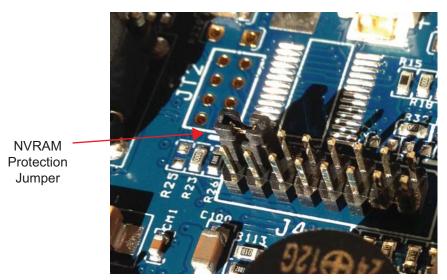

| 3-16         | NVRAM Protection Jumper                                                     | 47   |

| Chapte       | r 4 PowerDNA Explorer                                                       | . 48 |

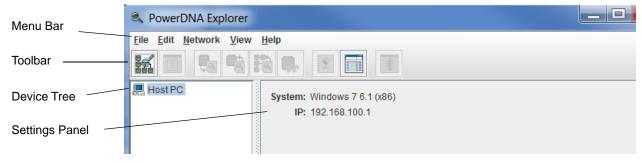

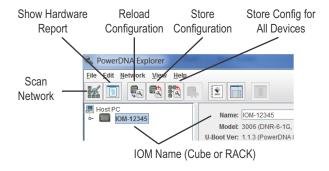

| 4-1          | PowerDNA Explorer                                                           |      |

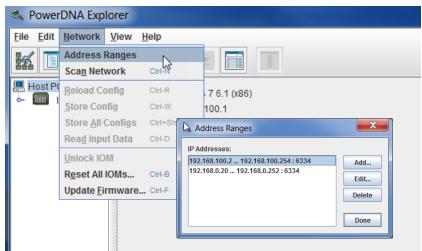

| 4-2          | Address Ranges to be Scanned                                                | 49   |

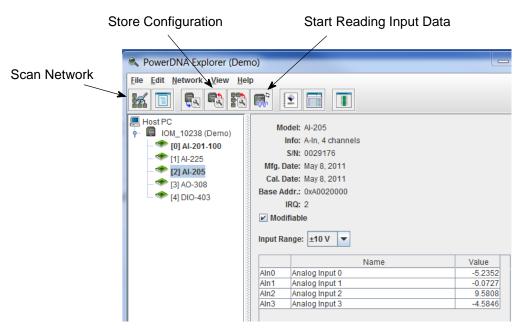

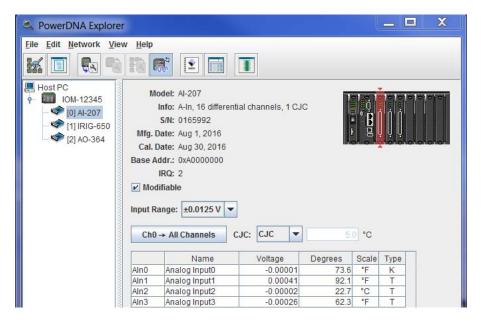

| 4-3          | Typical Screen for Analog Input Board                                       | 50   |

| 4-4          | PowerDNA Explorer Main Window                                               |      |

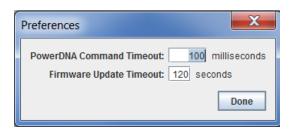

| 4-5          | PowerDNA Explorer Timeout Preferences                                       |      |

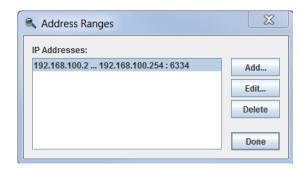

| 4-6          | Address Ranges Dialog Box                                                   |      |

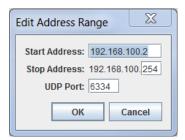

| 4-7          | Edit Address Ranges Dialog Box                                              |      |

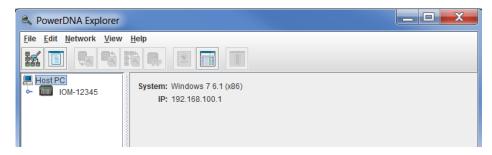

| 4-8          | After a Network >> Scan Network                                             |      |

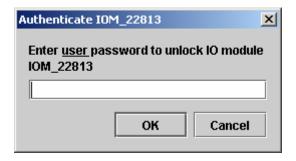

| 4-9          | Password Dialog Box for "Store Config" and "Store All Configs"              |      |

| 4-10         | Password Dialog Box for "Update Firmware"                                   |      |

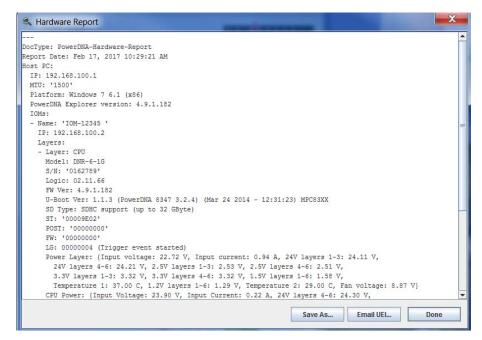

| 4-11         | Example of a Hardware Report                                                |      |

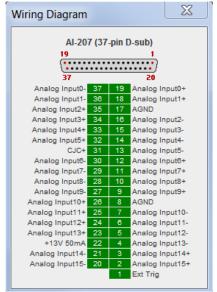

| 4-12         | Example of a Wiring Diagram Display                                         |      |

| 4-13         | PowerDNA Explorer Toolbar Buttons (Config Level)                            |      |

| 4-14         | PowerDNA Explorer Toolbar Buttons (Board Level)                             |      |

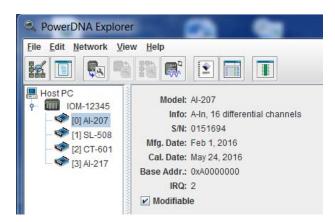

| 4-15<br>4-16 | Example of IOM Settings Panel                                               |      |

| 4-16         | Example of I/O Davise Settings                                              |      |

| 4-17         | Example of I/O Device Settings                                              |      |

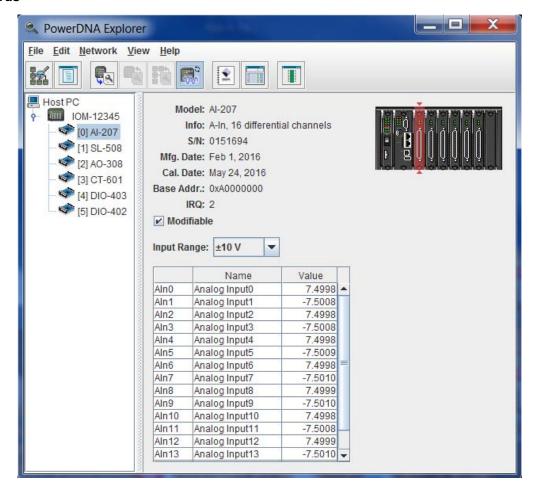

| 4-18<br>4-10 | Screen from Network >> Read Input Data                                      |      |

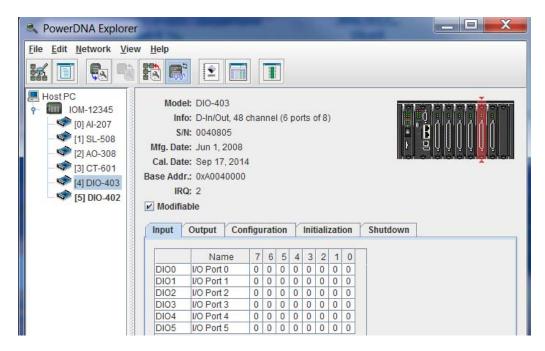

| 4-19<br>4-20 | Example of DIO-403 Inputs                                                   |      |

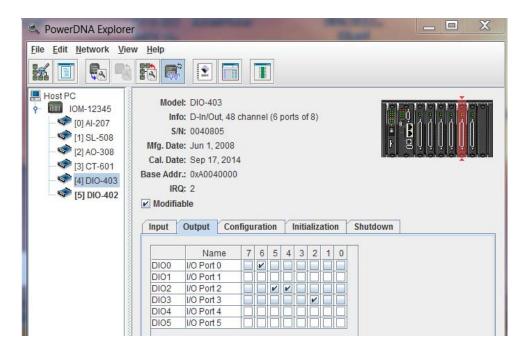

| 4-20         | Example of DIO-403 Outputs                                                  |      |

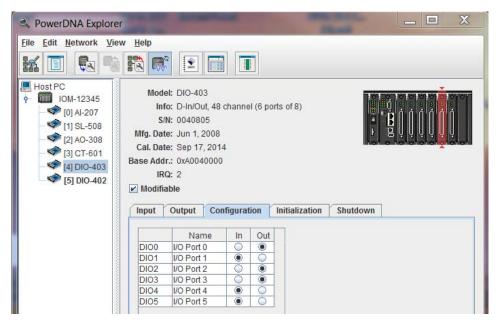

| 4-21         | Example of DIO-403 Configuration                                            | 03   |

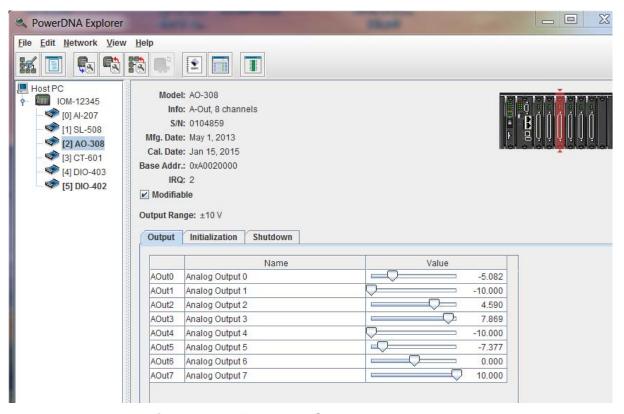

| 4-22  | Example AO-308 Board                            | 64 |

|-------|-------------------------------------------------|----|

| 4-23  | Example Al-207 Board                            | 65 |

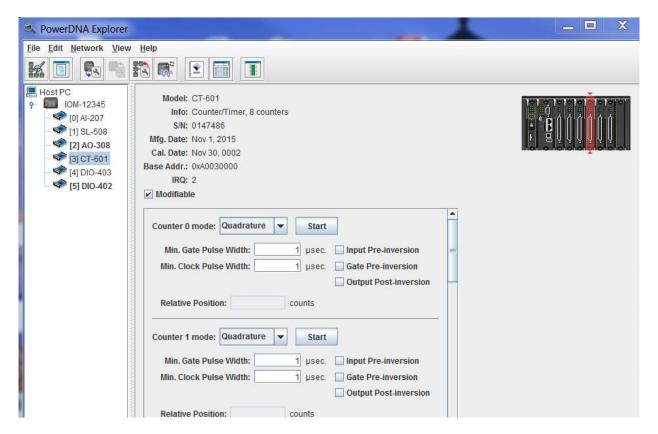

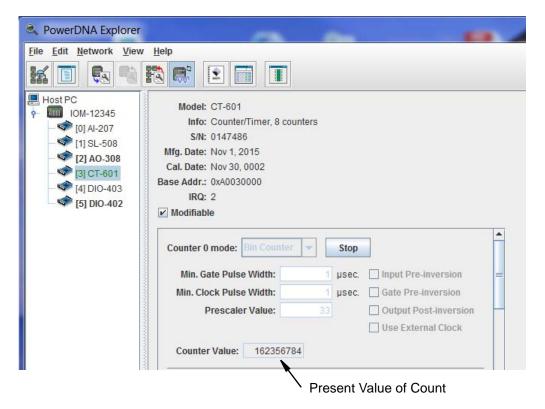

| 4-24  | Example CT-601 Board                            | 66 |

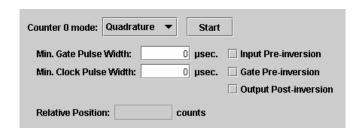

| 4-25  | Example Quadrature Controls                     |    |

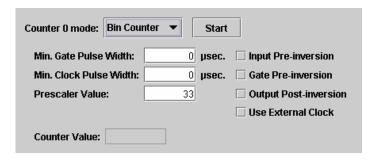

| 4-26  | Example Bin Counter Controls                    | 67 |

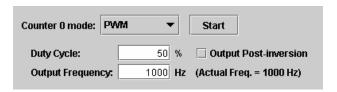

| 4-27  | Example Pulse Width Modulation (PWM) Controls   | 67 |

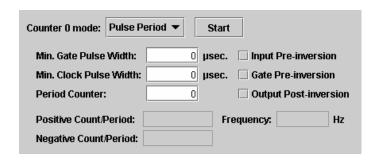

| 4-28  | Example Pulse Period Controls                   | 67 |

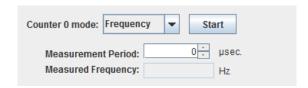

| 4-29  | Example Frequency Controls                      | 67 |

| 4-30  | Example of Started Counter                      | 68 |

| Chapt | ter 5 Programming CPU Board-specific Parameters | 69 |

| Apper | ndix A                                          | 81 |

| Apper | ndix B                                          | 85 |

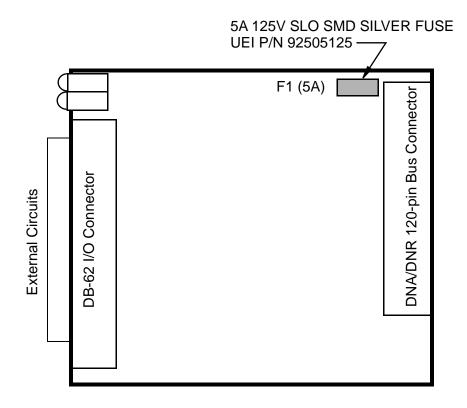

| B-1   | Location of Fuse for Fuse-Equipped Base Boards  | 85 |

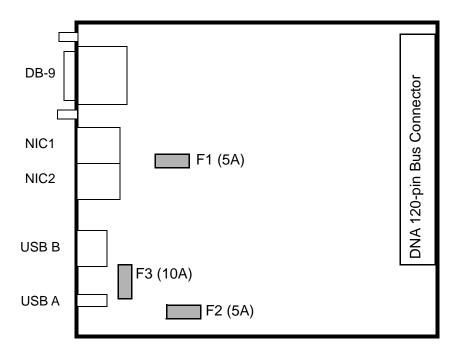

| B-2   | Location of Fuses for DNA-POWER-1GB Board       |    |

| Index |                                                 | 87 |

### **List of Tables**

| Chapte | r 1 Introduction                                        | 1  |

|--------|---------------------------------------------------------|----|

| 1-1    | Summary of DNA-PPCx-1G / UEINet CPU Versions            | 3  |

| Chapte | r 2 The PowerDNA DNA-PPCx-1G Cube System Description    | 4  |

| 2-1    | PowerDNA 1G Cube Front Panel Descriptions               | 9  |

| 2-2    | System Status LED Descriptions                          |    |

| 2-3    | Components in PowerDNA Core Module (DNA-PPC-1GB Series) |    |

| 2-4    | DC Power Thresholds for DNA-PPCx-1G Cubes               | 14 |

| Chapte | r 3 Installation and Configuration                      | 16 |

| 3-1    | DNA-PPCx-1G Cube Dimensions                             |    |

| 3-2    | Port States                                             |    |

| 3-3    | Example Functions and Associated Boards                 | 44 |

| Chapte | r 4 PowerDNA Explorer                                   | 48 |

| 4-1    | Fields and Descriptions for IOM Settings Panel          |    |

| Chapte | r 5 Programming CPU Board-specific Parameters           | 69 |

| 5-1    | Memory Map for DNA-PPCx-1G CPU (-00/-01 CPU)            |    |

| 5-2    | Memory Map for DNA-PPCx-1G-02 CPU (-02 CPU)             | 70 |

| 5-3    | Memory Map for DNA-PPCx-1G-03 CPU (-03 CPU)             | 70 |

| 5-4    | Set Parameters                                          | 74 |

| Append | A xib                                                   | 81 |

| Append | dix B                                                   | 85 |

| B-1    | DNA/DNR Replacement Fuses                               |    |

| Index  |                                                         | 87 |

### **Chapter 1** Introduction

This document describes the features, performance specifications, and operating functions of the PowerDNA® DNA-PPCx-1G Gigabit Ethernet Cube data acquisition systems:

- UEINet<sup>™</sup> (single I/O board system)

- DNA-PPC5-1G (up to 3 I/O board system)

- DNA-PPC8-1G (up to 6 I/O board system)

- DNA-PPC9-1G (up to 7 I/O board system)

All systems are designed for use with a Gigabit Ethernet 1000Base-T communication network.

This chapter provides the following information:

- · Organization of This Manual (Section 1.1)

- Manual Conventions (Section 1.2)

- Product Versions (Section 1.3)

## 1.1 Organization of This Manual

This DNA-PPCx-1G User Manual is organized as follows:

- Chapter 1 Introduction

- This chapter describes the organization of the document and the conventions used throughout the manual.

- Chapter 2 PowerDNA 1G Cube System Description

This chapter provides an overview of our 1G Cube systems

(DNA-PPCx-1G / UEINet), component modules, features, accessories, and a list of all items you need for initial operation.

- Chapter 3 Installation and Configuration

This chapter summarizes the recommended procedures for installing, configuring, starting up, and troubleshooting a PPCx-1G system.

- Chapter 4 PowerDNA Explorer for the PPCx-1G

This chapter provides an introduction to the menus and screens of UEI's GUI-based communication application, PowerDNA Explorer.

- Chapter 5 Programming CPU Board-specific Parameters

This chapter describes tools and facilities used for reading and writing CPU board parameters.

- Appendix A Configuring Additional Ethernet Cards

This appendix describes procedures for installing and configuring Ethernet cards for use with Windows operating systems.

- Appendix B Field Replacement of Fuses

- Index

- This is an alphabetical listing of topics covered in the manual, identified by page number.

## 1.2 Manual Conventions

To help you get the most out of this manual and our products, please note that we use the following conventions:

Tips are designed to highlight quick ways to get the job done, or reveal good ideas you might not discover on your own.

**NOTE:** Notes alert you to important information.

**CAUTION!** advises you of precautions to take to avoid injury, data loss, and damage to your boards or a system crash.

Text formatted in **bold** typeface generally represents text that should be entered verbatim. For instance, it can represent a filenames, as in the following example: "You can instruct users how to run setup using **setup.exe** executable."

Bold typeface will also represent button names, as in "Click Scan Network."

Text formatted in fixed typeface generally represents commands, source code, or other text that should be entered verbatim into the source code, initialization, or other file or at a command prompt.

### Before you begin:

Before plugging any I/O connector into the Cube or Board, be sure to remove power from all field wiring. Failure to do so may cause severe damage to the equipment.

### Usage of Terms

Throughout this manual, the term "Cube" and/or "DNA-PPCx-1G" refers to all PowerDNA Gigabit Ethernet Cube products:

- UEINet (-00/-01), DNA-PPC5-1G, DNA-PPC8-1G, DNA-PPC9-1G

- UEINet-02, DNA-PPC5-1G-02, DNA-PPC8-1G-02, DNA-PPC9-1G-02

- UEINet-03, DNA-PPC5-1G-03, DNA-PPC8-1G-03, DNA-PPC9-1G-03

Differences between product versions are noted on the following page.

Note that the -02 Cube version is a fully compatible upgrade of the -00/-01 Cube version.

## 1.3 Product Versions

This user manual provides documentation for the following product versions of the PowerDNA Gigabit Ethernet Cube:

- Cube with 1 I/O board: UEINet, UEINet-02, UEINet-03

- up to 3 I/O boards: DNA-PPC5-1G, DNA-PPC5-1G-02, DNA-PPC5-1G-03

- up to 6 I/O boards: DNA-PPC8-1G, DNA-PPC8-1G-02, DNA-PPC8-1G-03

- up to 7 I/O boards: DNA-PPC9-1G, DNA-PPC9-1G-02, DNA-PPC9-1G-03

Differences in -00/-01, -02, and -03 Cube versions are summarized in **Table 1-1**. Refer to the following chapters in this manual for detailed descriptions.

| Item                | Summary of Features                                                                        |

|---------------------|--------------------------------------------------------------------------------------------|

| DNA-PPCx-1G         | 10/100/1000Base-T Ethernet interface                                                       |

| UEINet<br>(-00/-01) | Freescale MPC8347 CPU                                                                      |

| ( 00/ 01)           | <ul> <li>1PPS synchronization support<sup>1</sup></li> </ul>                               |

|                     | • 128 MB RAM <sup>2</sup>                                                                  |

|                     | • 32 MB flash memory <sup>2</sup>                                                          |

| DNA-PPCx-1G-02      | 10/100/1000Base-T Ethernet interface                                                       |

| UEINet-02           | Freescale MPC8347 CPU                                                                      |

|                     | <ul> <li>1PPS/IEEE-1588 synchronization support<sup>1</sup></li> </ul>                     |

|                     | <ul> <li>Optional solid-state hard drives<sup>3</sup></li> </ul>                           |

|                     | • 256 MB RAM <sup>2</sup>                                                                  |

|                     | • 32 MB flash memory <sup>2</sup>                                                          |

| DNA-PPCx-1G-03      | 10/100/1000Base-T Ethernet interface                                                       |

| UEINet-03           | <ul> <li>Freescale MPC8347E CPU, (encryption-ready / IPSec support<br/>pending)</li> </ul> |

|                     | 1PPS/IEEE-1588 synchronization support <sup>1</sup>                                        |

|                     | <ul> <li>Optional solid-state hard drives<sup>3</sup></li> </ul>                           |

|                     | • 256 MB RAM <sup>2</sup>                                                                  |

|                     | • 128 MB flash memory <sup>2</sup>                                                         |

### Table 1-1 Summary of DNA-PPCx-1G / UEINet CPU Versions

- 1.1PPS and IEEE-1588 synchronization support is described in the PowerDNx 1PPS Sync Interface Manual.

- 2.RAM and flash memory are not user-accessible for PowerDNA applications (hosted deployment). Portions of RAM and flash are available for UEIPAC-based systems (stand-alone deployment). See UEIPAC documentation for more information.

- 3.On UEIPAC-based systems (stand-alone deployment), solid state drives are used for data and/or root file system storage. See UEIPAC documentation for more information.

**NOTE:** The -02 version of the CPU board is a fully compatible upgrade of the -00/-01 CPU board version.

## Chapter 2 The PowerDNA DNA-PPCx-1G Cube System Description

This chapter provides the following information about the PowerDNA DNA-PPCx-1G and UEINet systems:

- PowerDNA Gigabit Ethernet Cube Overview (Section 2.1)

- Specifications (Section 2.2)

- Key Features (Section 2.3)

- PowerDNA DNA-PPCx-1G Cube Enclosure (Section 2.4)

- Front Panel Ports, Connections & LEDs (Section 2.5)

- PowerDNA CPU/POWER Core Module (Section 2.6)

- PowerDNA I/O Boards (Section 2.7)

## 2.1 PowerDNA Gigabit Ethernet Cube Overview

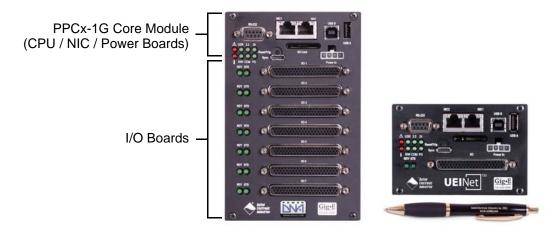

The UEI PowerDNA DNA-PPCx-1G and UEINet Cube products are Gigabit Ethernet Cube versions of our Ethernet-based data acquisition systems.

Each DNA-PPCx-1G and UEINet Cube houses a data acquisition system in a Cube chassis that can accept a set of user-selected I/O boards:

- UEINet accepts 1 user-selected I/O board

- DNA-PPC5-1G accepts up to 3 user-selected I/O boards

- DNA-PPC8-1G accepts up to 6 user-selected I/O boards

- DNA-PPC9-1G accepts up to 7 user-selected I/O boards

Figure 2-1. UEI PowerDNA DNA-PPC9-1G & UEINet Systems

**NOTE:** As an option for rackmount solutions, up to 4 Cube systems can be mounted in UEI's DNA-19RACKW accessory assembly.

A standard PowerDNA Cube consists of the following modules:

- One Cube enclosure (UEINet or DNA-PPC5-1G, DNA-PPC8-1G, DNA-PPC9-1G)

- One DNA-PPC-1GB CPU module (top slot)

- One DNA-POWER-1GB DC power module (second slot)

- Selection of DNA I/O boards

- DNA-IO-FILLER panels (one for each unused I/O slot)

- DNA-PSU-24-100 100-Watt, 120/230 VAC to +24VDC External Power Supply with cable and Molex connector

To configure a complete data acquisition system, specify up to 7 DNA I/O boards for installation into your Cube enclosure. I/O boards may be specified in any combination of UEI's DNA I/O boards.

**NOTE:** For detailed descriptions of all I/O boards and accessories available for DNA-PPCx-1G and UEINet Cubes, refer to www.ueidaq.com.

UEI stand-alone systems (UEIPAC, UEISIM, UEIModbus, and UEIOPCUA deployments) are also available for use with PowerDNA Gigabit Cube systems:

- UEIPAC XXX-1G Programmable Automation Controller

- UEISIM XXX-1G Simulink / Simulink Coder Target

- UEIModbus XXX-1G Modbus TCP-based Controller

- UEIOPCUA XXX-1G OPC-UA Server, accessed by any OPC-UA client

## 2.2 Specifications

Figure 2-2 lists the technical specifications for the DNA-PPCx-1G cubes.

| Standard Interfaces          |                                                                                                                       |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Gigabit Ethernet             | Two independent 1000/100/10Base-T interfaces, each with a unique IP address (connected via standard RJ-45 connectors) |

| USB 2.0                      | not supported in DNA-PPCx-1G Cubes                                                                                    |

| Config/General               | RS-232, 9-pin "D"                                                                                                     |

| Sync                         | Custom cable to sync multiple cubes                                                                                   |

| I/O Slots Available          |                                                                                                                       |

| UEINet                       | 1 slot (4.0" x 4.1" x 2.7")                                                                                           |

| DNA-PPC5-1G                  | 3 slots (4.0" x 4.1" x 4.0")                                                                                          |

| DNA-PPC8-1G                  | 6 slots (4.0" x 4.1" x 5.8")                                                                                          |

| DNA-PPC9-1G                  | 7 slots (4.0" x 4.1" x 6.6")                                                                                          |

| <b>Host Communication</b>    | IS .                                                                                                                  |

| Distance from host           | 100 meters max, CAT5+ cable                                                                                           |

| Ethernet data transfer rate  | 20 megabyte per second                                                                                                |

| Analog data<br>transfer rate | >6 megasample per second. Capable of sustained transfer of any cube configuration                                     |

| DMAP I/O mode                | update 1000 I/O channels (analog and/or digital) in less than 1 millisecond, guaranteed                               |

| Processor                    |                                                                                                                       |

| CPU                          | Freescale 8347 series, 400 MHz, 32-bit (8347E optional)                                                               |

| Memory                       | 128 MB (not including on-board Flash)                                                                                 |

| Status LEDs                  | Attention, Read/Write, Power, Communications Active                                                                   |

| Environmental                |                                                                                                                       |

| Temp (operating)             | Tested to -40 °C to 70 °C                                                                                             |

| Temp (storage)               | -40 °C to 85 °C                                                                                                       |

| Humidity                     | 0 to 95%, non-condensing                                                                                              |

| Vibration                    |                                                                                                                       |

| (IEC 60068-2-64)             | 10–500 Hz, 3 <i>g</i> (rms), Broad-band random                                                                        |

| (IEC 60068-2-6)              | 10–500 Hz, 3 <i>g</i> , Sinusoidal                                                                                    |

| Shock                        |                                                                                                                       |

| (IEC 60068-2-27)             | 100 g, 3 ms half sine, 18 shocks at 6 orientations; 30 g, 11 ms half sine, 18 shocks at 6 orientations                |

| Altitude                     | 70,000 feet, maximum                                                                                                  |

| MTBF                         | 160,000 hours                                                                                                         |

| <b>Power Requirements</b>    |                                                                                                                       |

| Voltage                      | 9 - 36 VDC (AC adaptor included)                                                                                      |

| Power Dissipation            | 8 W at 24 VDC (not including I/O boards)                                                                              |

Figure 2-2. Technical Specifications

### **2.3 Key Features** The following table is a list of key features of the DNA-PPCx-1G cubes.

#### Easy to configure and deploy

- Over 70 different I/O boards available

- Built-in signal conditioning

- Gigabit Ethernet based (100/10Base-T compatible)

- Flange kit for mounting to wall/flat surface

- DIN rail and Rack Mount kits

- Standard "Off-the-shelf" products and delivery

#### **True Real-time Performance**

- 1 msec updates guaranteed with 1000 I/O

- Up to 6 million samples per second

- Use QNX, RTX, VxWorks

### **Flexible Connectivity**

- Dual 1000Base-T Gigabit Ethernet ports with independent IPs

- Dual USB 2.0 controller ports (not supported in PowerDNA deployments)

- 10/100Base-FX Fiber interface available (see DNA-FPPC family)

- Supports WIFI / GSM / Cell networks

#### **Compact Size:**

- 4.1" x 4" x 6.6 Cube holds 7 I/O boards

- 4.1" x 4" x 5.8" Cube holds 6 I/O boards

- 4.1" x 4" x 4.0" Cube holds 3 I/O boards

- 4.1" x 4" x 2.7" Cube holds 1 I/O board

- up to 175 analog inputs per cube

- up to 224 analog outputs per cube

- up to 336 digital I/O bits per cube

#### **Rugged and Industrial:**

- All Aluminum construction

- Operation tested from -40°C to 70°C

- Vibration tested to 3 g, (operating)

- Shock tested to 100 g, (operating)

- All I/O isolated from Cube and host PC

- Operation to 70,000 feet

#### **Outstanding Software support**

- Windows, Linux, RTX, VxWorks and QNX operating systems

- VB, VB .NET, C, C#, C++

- MATLAB, LabVIEW, OPC, ActiveX support

Figure 2-3. Product Features

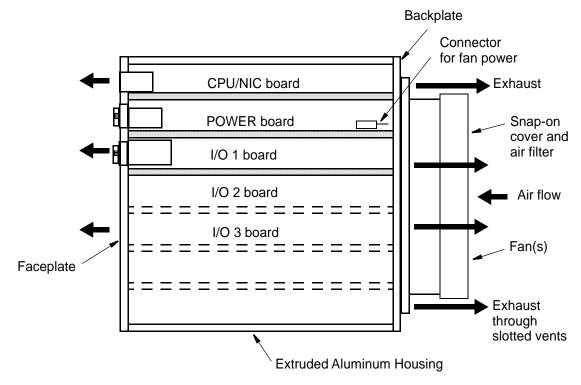

### 2.4 PowerDNA DNA-PPCx-1G Cube Enclosure

The cube enclosure is a rigid, extruded aluminum, mechanical structure with complete EMI shielding. Unused slots are filled with blank filler panels.

The DNA-PPCx-1G cube enclosure houses the following components:

- One DNA-PPC-1GB CPU module (slot 1)

- A DNA-POWER-1GB DC/DC power module (slot 2)

- PowerDNA I/O boards (slot 3 through slot 9, where the number of supported boards depends on the product version)

- · Blank filler panels for unused slots

- Up to two 8-volt cooling fans mounted on the rear cover of the cube

Behind the faceplate, the Power / CPU / IO board stack is positioned in the cube chassis on grooved guides.

The DC power module provides output voltages of 24, 3.3, 2.5, 1.5, and 1.2 VDC for the logic/CPU and 8 VDC to power the cooling fans.

### 2.4.1 Fans & Air Flow

**Figure 2-4** shows a representation of air flow through the PowerDNA cube.

Air is drawn into the rear of the enclosure, routed forward over the electronic circuit boards, up to the top of the enclosure, and then out the top rear of the enclosure. The system is designed to maintain positive pressure cooling within the enclosure at all times.

Figure 2-4. Air Flow through PowerDNA Cube

A temperature sensor mounted on the POWER board above the CPU monitors temperature within the cube. The system turns on the fan(s) if the temperature exceeds 45° C and shuts down power to the cube if a high limit is exceeded.

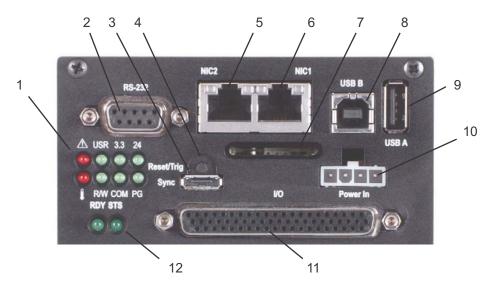

## 2.5 Front Panel Ports, Connections & LEDs

The ports and LEDs of the CPU / Power core module are illustrated in Figure 2-5 and described in **Table 2-1**.

A block diagram of the DNA-PPCx-1G core and additional descriptions of CPU / Power components are provided in Section 2.6 on page 11.

Note that the USB ports and the SD card are not supported in PowerDNA (hosted) deployments (USB ports and the SD card are supported in our UEIPAC-based systems, which are embedded, stand-alone products).

Figure 2-5. PowerDNA 1G Cube Front Panel Arrangement

| No. | Name                     | Description                                                                                                          |

|-----|--------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1   | Status LEDs              | See Figure 2-6 and <b>Table 2-2</b> for LED descriptions                                                             |

| 2   | RS-232 port <sup>1</sup> | DB-9 serial connector for configuration or troubleshooting. Connection runs at 57,000 bps, 8 bits, no parity, 1 stop |

| 3   | Sync port <sup>1,2</sup> | High-speed, Cube-to-Cube connector for multi-cube synchronization                                                    |

| 4   | Reset                    | Recessed reset button                                                                                                |

| 5   | NIC2                     | Diagnostic Ethernet port: NIC2<br>1000/100/10Base-T connection                                                       |

| 6   | NIC1                     | Primary Ethernet port: NIC1<br>1000/100/10Base-T connection                                                          |

| 7   | SD card slot             | SD card slot (for use with UEIPAC-based (embedded, stand-alone) systems, not supported on PowerDNA deployments)      |

| 8   | USB B                    | USB B controller port (not user-accessible on PowerDNA deployments)                                                  |

| 9   | USB A                    | USB A slave port (not user-accessible on PowerDNA deployments)                                                       |

Table 2-1. PowerDNA 1G Cube Front Panel Descriptions

| No. | Name                   | Description                                                                              |

|-----|------------------------|------------------------------------------------------------------------------------------|

| 10  | Power-In <sup>1</sup>  | Power In 4-pin molex connector: 9-36 VDC, DNA-PSU adapter included                       |

| 11  | I/O board connector(s) | DB-37 or DB-62 connection(s) to I/O board(s) (See I/O board manuals for pinout diagrams) |

| 12  | I/O board LEDs         | I/O board LEDs: RDY (ready), STS (active)                                                |

Table 2-1. PowerDNA 1G Cube Front Panel Descriptions (Cont.)

- 1. See Section 3.7.2 on page 38 for RS-232, sync, and power connector pinout diagrams.

- 2. Refer to the *PowerDNx 1PPS Synchronization Interface Manual* for more information about 1PPS or IEEE-1588 / PTP programming.

Status LEDs are displayed in **Figure 2-6** and described in **Table 2-2**. LEDs are physically mounted on the POWER module.

Figure 2-6. DNA-PPCx-1G Front Panel LEDs

| No. | Name     | Description                                                                               |

|-----|----------|-------------------------------------------------------------------------------------------|

| 1   | ATT      | Indicates system needs attention: Error when red LED is ON                                |

| 2   | USR      | Optionally controlled by user application: OFF is default                                 |

| 3   | 3.3      | Indicates status of internal 3.3 V supply: LED ON (OK) / OFF (ERROR)                      |

| 4   | 24       | Indicates status of internal 24 V supply: LED ON (OK) / OFF (ERROR)                       |

| 5   | PG       | Indicates the presense of a valid power input: LED ON (OK) / OFF (ERROR)                  |

| 6   | СОМ      | Indicates I/O communication active: Flashes once/second when communicating / OFF when not |

| 7   | R/W      | Indicates bus activity: Flashes when bus is active / OFF when not                         |

| 8   | OverTemp | Indicates high temperature condition in module: LED ON (high temp) / OFF when not         |

Table 2-2. System Status LED Descriptions

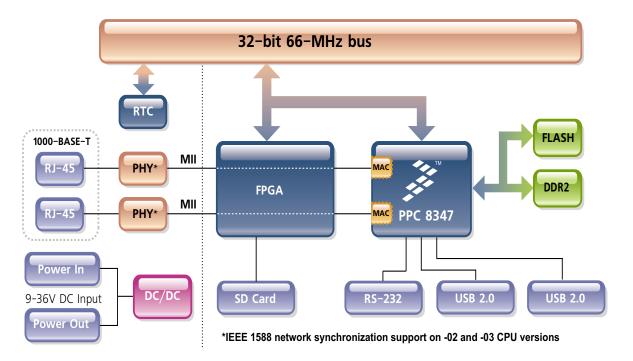

### 2.6 PowerDNA CPU/POWER Core Module

The DNA-PPCx-1G core is a 2-board module that consists of a CPU/NIC board and a POWER board. It is assembled in the upper two slots a PPCx-1G cube.

- The CPU/NIC board contains a Freescale PowerPC 8347 400 MHz, 32-bit CPU and associated Network Interface Control (NIC) logic that controls all Ethernet communication.

- The DNA-POWER-1GB board uses a dedicated DC/DC source to provide power to the PowerDNA PPCx-1G cube.

DNA-PPCx-1G core components are shown in the functional block diagram in **Figure 2-7** below and described in **Table 2-3**.

Figure 2-7. Functional Block Diagram of DNA-PPCx-1G Core Module (2 Boards)

Table 2-3 Components in PowerDNA Core Module (DNA-PPC-1GB Series)

| Item                                         | Description                                                                                                                                                                                                            |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NIC1                                         | The NIC1 port provides communication between the Cube system and the primary LAN network.                                                                                                                              |

| NIC2                                         | The NIC2 port provides the ability to monitor the Cube system health during operation, using a separate diagnostic port. This port may also be assigned as the primary Ethernet port if NIC1 is not available for use. |

| RS-232 Port <sup>1</sup>                     | The RS-232 port provides a serial communication link between the Cube system and a standard RS-232 terminal.                                                                                                           |

| USB 2.0 Dual Ports<br>(Controller and Slave) | The USB A and B ports are not supported on DNA-PPCx-1G (hosted) systems (only supported on UEIPAC, UEISIM, UEIModbus, and UEIOPC-UA deployments).                                                                      |

Table 2-3 Components in PowerDNA Core Module (DNA-PPC-1GB Series)

| Item                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32 MB or 128 MB<br>Flash Memory                      | DNA-PPCx-1G / UEINet (-00/-01) systems provide 32 MB of flash memory. DNA-PPCx-1G-02 / UEINet-02 systems provide 32 MB of flash memory. DNA-PPCx-1G-03 / UEINet-03 systems provide 128 MB of flash memory. (Flash is only user-accessible on UEIPAC-based deployments)                                                                                                                                                                      |

| 128 MB or 256 MB<br>of SDRAM                         | DNA-PPCx-1G / UEINet (-00/-01) systems provide 128 MB of RAM. DNA-PPCx-1G-02 / UEINet-02 systems provide 256 MB of RAM. DNA-PPCx-1G-03 / UEINet-03 systems provide 256 MB of RAM. (SDRAM is only user-accessible on UEIPAC-based deployments)                                                                                                                                                                                               |

| SYNC Port <sup>1,2</sup>                             | A high-speed system-to-system synchronization connector permits triggers and/or clocks to be shared among multiple systems. Two systems may be connected together directly and larger groups may use the SYNC interface to share timing signals among many cubes and systems.                                                                                                                                                               |

|                                                      | The trigger and clock inputs will accept signals from standard digital logic that is powered in the range of 3.3V to 5V. The inputs also have internal pull-up resistors to an internal 5V supply, making the inputs also compatible with a low-side drive open-collector output. The Sync and trigger outputs have 5V logic levels. The sync connector's ground and 5V power connections are provided by its own isolated DC-DC converter. |

| IEEE-1588<br>Synchronization<br>Support <sup>2</sup> | DNA-PPCx-1G-02 / UEINet-02 and DNA-PPCx-1G-03 / UEINet-03 systems support IEEE-1588 synchronization in hardware.                                                                                                                                                                                                                                                                                                                            |

| SD Card                                              | A slot for inserting a Secure Digital card. SD cards are not supported on DNA-PPCx-1G systems. (SD cards are only supported on UEIPAC, UEISIM, UEIModbus, and UEIOPC-UA deployments; uses EXT3 as filesystem for the system partition and optionally FAT32 for one or more data partitions on the UEIPAC-based stand-alone systems only).                                                                                                   |

| Solid State Hard Drive                               | Optional solid state hard drive (only supported on UEIPAC, UEISIM, UEIModbus, and UEIOPC-UA deployments).                                                                                                                                                                                                                                                                                                                                   |

| LEDs                                                 | The operating conditions indicated by the front panel LEDs are described in Figure 2-6 on page 10.                                                                                                                                                                                                                                                                                                                                          |

- 1. See Section 3.7.2 on page 38 for sync and RS-232 port pinout diagrams.

- 2. 1PPS and IEEE-1588 synchronization support is described in the *PowerDNx 1PPS Sync Interface Manual*.

## 2.6.1 Key Features of the DNA-POWER-1GB Board

The DNA-POWER-1GB board provides a non-isolated side (NIS) logic that complies with full common logic interface (CLI) implementation.

The key features of the unit are:

- Input power 9-36 VDC 80 W maximum, protected by resettable fuses and EMI chokes

- Output power sources (all with greater than 90% efficiency)

24 V, 1 A (24 W)

3.3 V, 5 A (16.5 W, including the 2.5 V derived voltage)

2.5 V, 3 A (derived from 3.3 V source)

1.5 V, 5 A, (7.5 W, including the 1.2 V derived voltage)

8 V, 0.5 A (4 W for fans)

- DC/DC for 24 V, 3.3 V, and 1.5 V are synchronized from the single spread-spectrum clock source in the CPU/NIC Core Module for low EMI noise level

- Fan control (Forced ON) and status ON/OFF

- Monitoring and LED indicators (1% accuracy, 0.25Hz update rate) for

- All output voltages

- Input current for the 9-36 VDC for the DNA cube housing

- All voltages from the NIC/Power Module (24 V, 3.3 V, 2.5 V)

- Temperature of the DNA-PPCx cube housing and boards

- Provides 9-36 VDC for all modules from an external power source

## 2.6.2 DC Power Thresholds

Table 2-4 lists the DC power threshold specifications for PPCx-1G cubes.

Table 2-4. DC Power Thresholds for DNA-PPCx-1G Cubes

|                                            | Backplane<br>Power Rail<br>Voltages | Turn-on<br>Voltage, V <sup>1</sup> | Reset<br>Voltage, V | Turn-off<br>Voltage, V <sup>2</sup> | Notes                                                                                |

|--------------------------------------------|-------------------------------------|------------------------------------|---------------------|-------------------------------------|--------------------------------------------------------------------------------------|

| Logic<br>power supply                      | +3.3V,<br>+2.5V,<br>+1.5V,<br>+1.2V | 7.5                                | 7.2 <sup>3</sup>    | 7.0                                 | Supplies power to all CPUs and FPGAs                                                 |

| Analog<br>power supply                     | +24V                                | 8.5                                | -                   | 7.8                                 | Analog power supply is used as a regulated source for on-layer DC/DCs on most boards |

| Fan power supply                           | +12V                                | 8.5                                | -                   | 8.4                                 |                                                                                      |

| On-layer<br>DC/DCs that use<br>input power | +VIn                                | 7.8-8.8                            | -                   | 7.5-8.5                             | Varies with I/O board type                                                           |

- 1. Turn-on, V: The value of Vin at which the corresponding DC/DCs are turned on.

- 2. Turn-off, V: The value of Vin at which the corresponding DC/DCs are turned off.

- 3. Reset V: When Vin is below 7.2 V, a voltage reset puts all boards into reset mode.

NOTE: A DNA-PPC-1GB core module consumes 70 mW when Vin is below 7 V.

## 2.7 PowerDNAI/O Boards

PowerDNAI/O DNA-PPCx-1G I/O boards are identified with a DNA- prefix.

Your selection of I/O boards can include

- Analog input boards to measure voltage, current, strain gages, thermocouples and more

- Analog output boards with outputs to ±40 V or ±50 mA

- Digital I/O interfaces for logic and "real-world" signal levels

- · Counters and timers, quadrature encoder inputs

- Communications interfaces for RS-232, RS-422/485, ARINC 429/453/708, AFDX, MIL-STD-1553, CAN bus, and more

- · And more

I/O boards are populated into your Cube chassis in the order you specify.

Refer to the I/O board data sheets and user manuals for detailed electrical specifications, board descriptions, and user instructions. These documents are available on the UEI website at <a href="https://www.ueidaq.com">www.ueidaq.com</a>.

### I/O Board Stack Sequence in a Cube

Individual boards can be removed and replaced in the field. You can also rearrange the locations of boards within the cube enclosure at any time; however, note that you may need to move jumpers on the I/O board(s).

Each Cube I/O board includes a jumper block that identifies the I/O board position in the stack. If you change the order of your I/O boards in your Cube or install a new board, you may need to adjust corresponding hardware jumpers. This is only applicable in Cube systems (jumpers are not used in DNR or DNF I/O boards for installation in a RACKtangle or FLATRACK chassis.)

Refer to the *PowerDNA Field Installation Guide* for more information about installing I/O boards and setting jumper positions in cubes.

### **Chapter 3** Installation and Configuration

The following installation and configuration topics are included in this chapter:

- Initial Installation Guide (Section 3.1)

- Initial Boot-up(Section 3.2)

- IP Address Overview & Update Procedures (Section 3.3)

- Network Configuration (Section 3.4)

- Troubleshooting (Section 3.5)

- Updating Firmware (Section 3.6)

- Mounting and Field Connections (Section 3.7)

- Wiring I/O Boards (Section 3.8)

- Repairing / Upgrading a Cube System (Section 3.9)

- Configuring a NIC Port for Diagnostic Mode (Section 3.10)

- Disabling Writes to Flash/EEPROM (NVRAM) (Section 3.11)

## 3.1 Initial Installation Guide

This section describes the recommended procedure for initially setting up your hardware and software when you first receive a DNA-PPCx-1G system:

- Verify shipment contents, Section 3.1.1

- Install software, Section 3.1.2

- Verify communication over serial port (optionally) / initial boot up, Section 3.2

- Configure IP addresses (if needed), Section 3.3

- Connect your PowerDNA Cube to your host PC or network switch, Section 3.4 and Section 3.7 (optionally)

## 3.1.1 Inspect Package

With a standard DNA-PPCx-1G system, the shipping package should include the following:

- A DNA-PPCx-1G enclosure, preinstalled with a NIC/CPU module POWER module, blank filler panels (if needed), plus your selection of I/O boards

- A DNA-PSU-24-100 100-watt<sup>1</sup> universal powerline brick that plugs into an AC outlet and provides 24 VDC output. The supply comes with a power cord for the mains and an adapter cable ending in a Molex connector

- A DB-9 serial cable for initial hardware configuration and firmware downloading (DNA-DB9MF-CBL)

- A Cat5e Ethernet cable, 7 foot (DNA-CAT5E-CBL)

- CD-ROM with support software

<sup>1.</sup> A larger power supply may be required for some configurations. Refer to UEI.

### 3.1.2 Install Software

This section describes how to load the PowerDNA software suite onto a Windows- or Linux-based computer (i.e. host PC) and run some initial tests.

The latest support software is online at <a href="www.ueidaq.com/download">www.ueidaq.com/download</a>; a copy is also on the PowerDNA Software Suite CD.

### A. Software Install: Windows

The PowerDNA CD provides one installer that combines the UEI low-level driver and UEIDAQ Framework.

Be sure to install third-party applications (such as LabVIEW, MATLAB, or Visual Studio) *before* installing the PowerDNA Software Suite. The installer automatically searches for third-party IDE and testing suites, and adds them as tools to the suites found.

To install PowerDNA software, do the following:

**STEP 1:** Open the PowerDNA Software Suite installer as an administrator.

You can run the installer from the provided PowerDNA Software Suite CD or from a downloaded installation from our website.

To run the installer from the PowerDNA Software Suite CD, insert the CD into your CD-ROM drive. Windows should automatically start the PowerDNA Setup program.

An installer with the UEI logo will open, and then the PowerDNA Welcome screen should appear.

If this does not happen, run setup.exe from the CD drive:

### Start >> Run >> d:\setup.exe >> OK

- To run from a recently downloaded executable from www.ueidaq.com, right-click the filename, and run as administrator.

- **STEP 2:** Follow the prompts, and then choose a PowerDNA Software Suite Setup Type.

Unless you are an expert user and have specific requirements, select *Typical Installation* and accept the default configuration.

The Software Suite installer automatically installs any required tools and plugins. If 32-bit Java VM is not detected on the system, Java JRE 1.6.5 for Windows XP will automatically be installed for PowerDNA Explorer. As an alternative, use the *Custom* option to display and ensure that all of the necessary packages are installed.

- Companion Documentation:

- Quick Start Guide, Configuration and Core Module, I/O Board Manuals, API Programming Guide

- SDK: includes/lib for C/Java, examples, and JRE;

(The SDK is not the UeiDaq Framework)

- PowerDNA Apps: PowerDNA Explorer, MTTTY

- PowerDNA Components (incl. DLL files)

- PowerDNA Firmware

- **STEP 3:** Click **Next** to continue through the dialogs.

### **STEP 4:** Click **Finish** to complete the installation.

The Software Suite installs tools needed in later steps, such as MTTTY, PowerDNA Explorer, and the low-level driver.

UEIDAQ Framework is also included in the installation and provides the structure for developing applications under C/C++, C#, VB.NET, ActiveX, MATLAB, LabVIEW, LabWindows/CVI, OPC, and other programming languages.

### **STEP 5:** Restart the computer.

NOTE: Because the installation process modifies your Windows registry, you should always install or uninstall the software using the appropriate utilities. Never remove PowerDNA software from your PC directly by deleting individual files; always use the Windows Control Panel Add/Remove Programs utility.

### B. Software Install: Linux

The PowerDNA\_\*.tgz file in the CD\Linux folder contains the software package for Linux. To extract the file to a local directory:

```

tar -xjvf <Path to file>/PowerDNA*.tgz

```

Follow the instructions in the readme.txt file provided in the tar file.

- **3.2 Initial Boot-up** Perform an initial boot in preparation for configuring the network using the following procedure:

- **STEP 1:** Familiarize yourself with the layout of your DNA-PPCx-1G system front panel. Refer to Figure 2-5 on page 9 for board placement.

- **STEP 2:** Optionally, set up communication over the serial port by attaching the serial cable between the host PC and to the RS-232 port on the front panel of the DNA-PPCx-1G:

- a. Run a serial terminal-emulation program (e.g., MTTTY) on the PC. Any terminal-emulation program, except HyperTerminal, may be used (MTTTY, Minicom, TeraTerm, PuTTY, etc.).

- b. Verify that COM parameters are set at: 57600 baud, 8 bits, no parity, 1 stop bit.

- c. Click **Connect** in MTTTY, or use the commands on one of the other terminal-emulation programs to establish communication with the DNA-PPCx-1G system.

- **STEP 3:** Connect power to the system via the Molex connector at the front of the DNA-PPCx-1G chassis.

**NOTE:** As soon as the system powers up, it runs through a self-diagnostic mode and, if you have serial communications set up, generates output on the terminal program. A typical readout is shown below.

Figure 3-1. Typical MTTTY Screen after DNA-PPCx-1G Boot-up

The boot process displays the model, serial number, and slot positions of boards in the cube enclosure.

You can also type show <Return> at the DQ> serial prompt to display additional information about the system configuration:

```

DQ> show

name: "IOM-174257"

model: 3005

serial: 0174257

fwct: 1.2.0.0

mac: 00:0C:94:02:A8:B1

srv: 192.168.100.2

ip: 192.168.100.2 (1Gbit)

gateway: 192.168.100.1

netmask: 255.255.255.0

mac2: 00:0C:94:F2:A8:B1

srv2: 192.168.100.102

ip2: 192.168.100.102 (DOWN)

gateway2: 192.168.100.1

netmask2: 255.255.255.0

udp: 6334

license: ""

Manufactured 4/6/2017

Calibrated 4/6/2017

DQ>

```

Through the serial connection, all parameters can be changed, including the IP address, gateway, and subnet mask (netmask) system configuration.

The next section provides instructions for changing the IP address. You can also refer to **Chapter 5** for more information about changing the IP address and other parameters via the serial port.

## 3.3 IP Address Overview & Update Procedures

The DNA-PPCx-1G ships with pre-configured factory default IP addresses for NIC1 and NIC2 in nonvolatile memory (usually 192.168.100.2 for NIC1 and 192.168.100.102 for NIC2). These are static IP addresses; a hosted DNA-PPCx-1G system never retrieves its IP address from a DHCP server.

This section describes when and how to change the default IP addresses.

## 3.3.1 When Should You Change the IP Address?

You should change your IP address if you have multiple UEI chassis in your application or if your application has network addressing guidelines you must conform to.

Before connecting your DNA-PPCx-1G to a general-purpose (company domain) network, consider the following:

- High sampling rate measurements consume a lot of the available bandwidth.

- Some samples may be significantly delayed or entirely dropped (lost) due to network congestion, collisions or a slow switch.

- Whether a system will be accessed by multiple parties on a LAN.

- Whether multiple Cubes/RACKs/systems will operate (and interact) on the same network.

Alternatively, if you plan to use the system for high-speed measurements where high reliability is necessary, a direct connection between the host PC and the DNA-PPCx-1G NIC is recommended.

Refer to "Network Configuration" on page 24 for more information.

### 3.3.2 How to Change the Primary IP Address (NIC1)

You can use PowerDNA Explorer (a UEI-developed GUI application) or a serial terminal program to change the IP address.

The first step in changing the IP address is to consult your system or network administrator to obtain unused IP addresses.

You can change the IP address from the default using either of the following procedures:

- Section 3.3.2.1 (via PowerDNA Explorer, recommended)

- Section 3.3.2.2 (via the serial port)

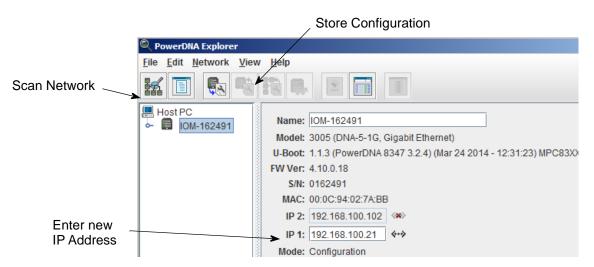

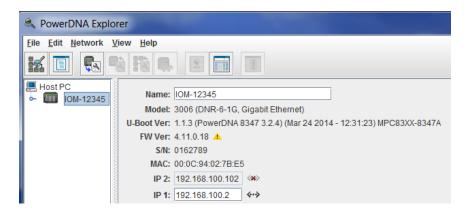

### 3.3.2.1 Update IP Address via PowerDNA Explorer

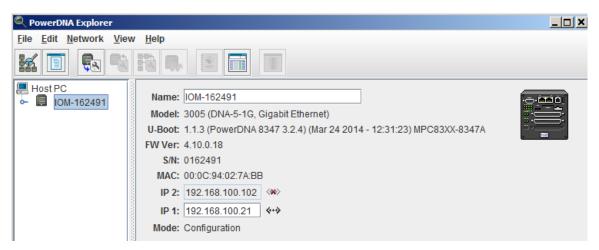

PowerDNA Explorer provides an interface for communicating with your DNA-PPCx-1G cube over an Ethernet connection.

To use PowerDNA Explorer, you must first establish communication between your host PC and chassis. Refer to **Chapter 4** for additional information about how to open, set up and use PowerDNA Explorer, if needed.

To update your IP address, do the following in the PowerDNA Explorer window:

- STEP 1: Click Scan Network to explore your system (refer to Figure 3-2 below).

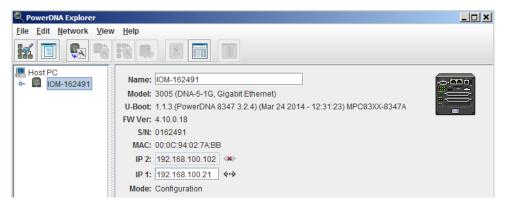

- **STEP 2:** Click the DNA-PPCx-1G system that you want to update, (e.g., IOM-162491. DNA-PPCx-1G systems are listed in the left panel).

- STEP 3: Enter the new IP address in the IP 1 field.

- **STEP 4:** Press <Return> on your keyboard.

- **STEP 5:** Click **Store Configuration** to save your change, and reset the DNA-PPCx-1G.

Figure 3-2. Using PowerDNA Explorer to Change IP Address

Storing the configuration downloads the new IP address into the system's non-volatile memory.

If needed, the gateway and network mask can be changed via the serial port. Refer to Section 5.4.3 on page 74 for instructions.

## 3.3.2.2 Update IP Address via Serial Port

To update the IP address on your DNA-PPCx-1G over the serial port, you must first establish serial communication between your host PC and chassis.

To set up communication over the serial port, do the following:

- a. Attach a serial cable between the host PC and the RS-232 port on the front panel of the DNA-PPCx-1G.

- b. Run a serial terminal-emulation program (e.g., MTTTY) on the PC. Any terminal-emulation program, except HyperTerminal, may be used (MTTTY, Minicom, TeraTerm, PuTTY, etc.).

- c. Verify that COM parameters are set at 57600 baud, 8 bits, no parity, 1 stop bit.

- d. Click **Connect** in MTTTY, or use the commands on one of the other terminal-emulation programs to establish communication with the DNA-PPCx-1G system.

**NOTE:** Once a connection is made, you will see a DQ> prompt when you press <Enter>.

To update the IP address on your DNA-PPCx-1G, enter the following commands in the serial terminal window:

```

DQ> set ip 192.168.200.65

Enter user password > powerdna

DQ> store

DQ> reset

```

Note that "192.168.200.65" is the new IP address in this example, the default password is "powerdna", and reset reboots the system, which is required for the new IP address to take effect.

To verify the update, you can type show to display the new IP address.

**NOTE:** Refer to **Chapter 5** for more descriptions of commands you can issue via a serial connection, including descriptions of the set and store commands.

Once your IP address is configured, you can connect the DNA-PPCx-1G NIC to your host PC or to a switch for communication via a network connection.

# 3.3.3 How to Change the Secondary (Diagnostic) IP Address (NIC2)

To change the IP address of the secondary port (NIC2), you use a serial terminal program as with the primary port, but instead use the command:

```

set ip2 aaa.bbb.ccc.ddd

```

where aaa.bbb.ccc.ddd is the new IP address for the secondary port.

Then proceed the same as with the primary port. NIC2 IP addresses cannot be changed using PowerDNA Explorer. Refer to **Chapter 5** for more information.

## 3.4 Network Configuration

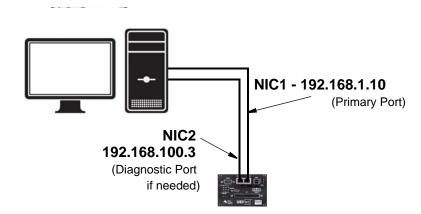

If you do not need to connect to a company LAN and have only a single DNA-PPCx-1G in your system, you can connect it directly to your host as shown in **Figure 3-3** below.

Figure 3-3. Single DNA-PPCx-1G Direct-Connected to Host without LAN Switch

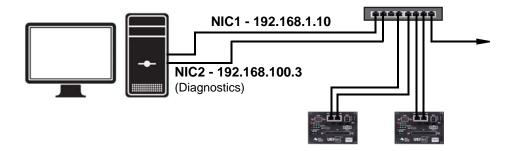

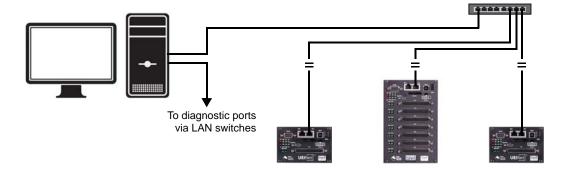

When connecting to a network, to improve DNA-PPCx-1G network performance, we recommend that instead of connecting to a company-wide network, you use separate commercially available network interface controller (NIC) cards and, where possible, set up a single dedicated mini-network for cubes for both operation and diagnostics, as shown in **Figure 3-4** below.

**Figure 3-4** shows a two-cube single network system with a LAN switch that performs both data acquisition and diagnostic functions.

Figure 3-4. Single Network for Operation and Diagnostics Using Cubes and One LAN Switch

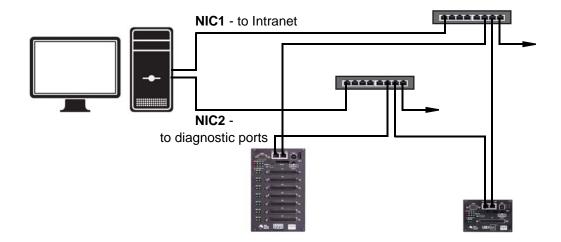

As an alternative, you can configure two separate networks, one for operation and one for diagnostic purposes, as shown in **Figure 3-5**.

**Figure 3-5** shows a two-cube dual network system that performs both data acquisition and diagnostic functions and uses two LAN switches for routing.

Figure 3-5. Separate Networks for Operation and Diagnostics:

Two Cubes & Two Switches

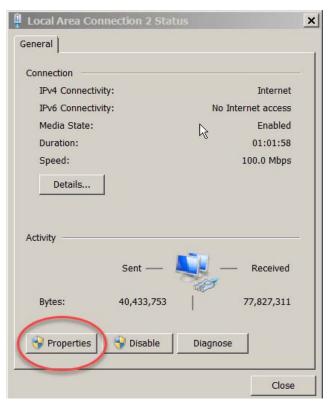

## 3.4.1 Example of Configuring Network Settings

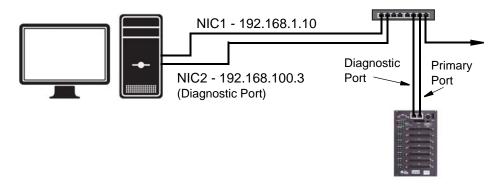

This section provides an example of configuring a separate network for diagnostics.

In this example, we assume that your office uses a Class C network (the class intended for small networks with fewer than 256 devices), and your host PC is configured with a static IP or via DHCP (Dynamic Host Configuration Protocol).

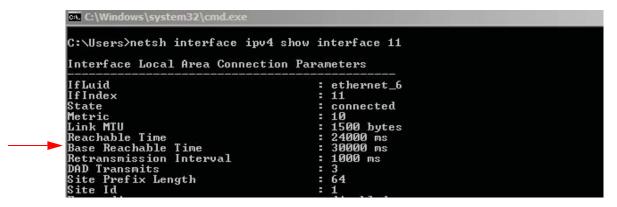

**STEP 1:** Obtain the networking configuration of your host PC:

• On Windows systems, open the command prompt and type <code>ipconfig</code> to display the configuration:

Start >> Programs >> (Accessories >>) Command Prompt

• On Linux systems, type ifconfig at the Linux prompt.

In the above example, the subnet mask of 255.255.255.0 uses the subnet range 192.168.1.0 through 192.168.1.255. Refer to the IP Addressing Side Note on the next page for more information about subnets.

### IP Addressing Side Note:

The range of usable addresses is defined by the IP address and subnet mask.

- An IP address is a number that lies within the range of 0.0.0.0 and 255.255.255.255.

In the ipconfig example shown in step 1, the IP address is 192.168.1.10.

- The subnet mask indicates where an address range starts and stops. For example, a subnet mask 255.255.255.240 has 15 usable addresses (255.255.255.255.255.255.255.240). In the ipconfig example shown in step 1, the subnet is 255.255.255.0, or 255 addresses.

The subnet limits from anything.anything.0 up to the max.

- The usable range for 192.168.1.10/255.255.255.0 is 192.168.1.1 to 192.168.1.254 (192.168.1.0 and 192.168.1.255 are reserved for Router and Broadcast messages).

- The usable range for 192.168.100.2/255.255.255.0 is 192.168.100.1 to 192.168.100.254

Not every IP address from 0.0.0.0 to 255.255.255.255 is usable; however, these three ranges of IP addresses are guaranteed open for private use:

- 10.0.0.0 10.255.255.255

- 172.16.0.0 172.31.255.255

- 192.168.0.0 192.168.255.255

- **STEP 2:** Install a secondary NIC card in your host PC, if needed.

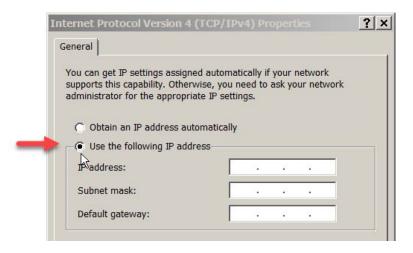

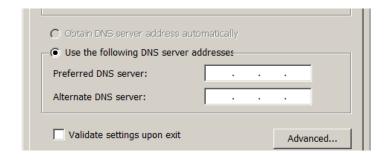

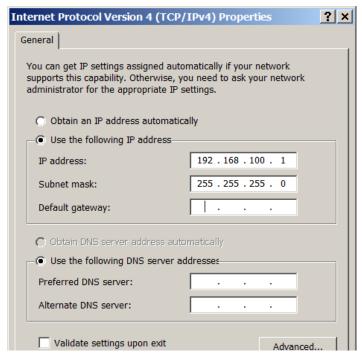

- **STEP 3:** Set up a secondary network that does not overlap the existing one:

In our example, the address space 192.168.1.0-192.168.1.255 is used by NIC1. The IP address block 192.168.100.1 to 192.168.100.255 is available and is in the private range.

We will choose 192.168.100.1-192.168.100.255 for the PC's secondary NIC and setup the port as follows:

```

IPv4 Address: 192.168.100.3

Subnet mask: 255.255.255.0

Default Gateway:192.168.100.3

```

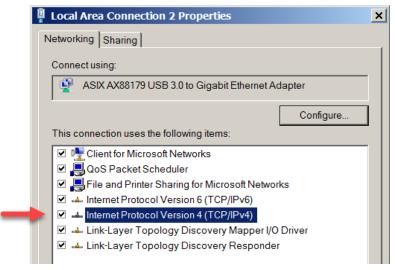

a. On your host PC, open the Network and Internet settings in the control panel:

Start >> Programs >> Control Panel >>Network and Internet >> View network status and tasks

- b. Click *Change adapter settings* in the left-sidebar, and then right-click the adapter to bring up the Properties window.