## DNx-429-516

## **User Manual**

16 ARINC-429 channels, configured as Receivers or Transmitters, plus 8 dedicated ARINC-429 Receiver-only channels

> Interface board with Guardian functionality for the PowerDNA Cube and RACK series chassis

#### February 2019

PN Man-DNx-429-516

© Copyright 2019 United Electronic Industries, Inc. All rights reserved.

Information furnished in this manual is believed to be accurate and reliable. However, no responsibility is assumed for its use or for any infringement of patents or other rights of third parties that may result from its use.

All product names listed are trademarks or trade names of their respective companies.

See the UEI website for complete terms and conditions of sale: http://www.ueidaq.com/cms/terms-and-conditions/

CE

#### **Contacting United Electronic Industries**

#### Mailing Address:

27 Renmar Avenue Walpole, MA 02081 U.S.A.

For a list of our distributors and partners in the US and around the world, please contact a member of our support team:

#### Support:

| Telephone:      | (508) 921-4600                                    |

|-----------------|---------------------------------------------------|

| Fax:            | (508) 668-2350                                    |

| Also see the FA | Qs and online "Live Help" feature on our web site |

#### Internet Support:

| Support:  | support@ueidaq.com   |

|-----------|----------------------|

| Website:  | www.ueidaq.com       |

| FTP Site: | ftp://ftp.ueidaq.com |

#### **Product Disclaimer:**

#### WARNING!

### DO NOT USE PRODUCTS SOLD BY UNITED ELECTRONIC INDUSTRIES, INC. AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

Products sold by United Electronic Industries, Inc. are not authorized for use as critical components in life support devices or systems. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. Any attempt to purchase any United Electronic Industries, Inc. product for that purpose is null and void and United Electronic Industries Inc. accepts no liability whatsoever in contract, tort, or otherwise whether or not resulting from our or our employees' negligence or failure to detect an improper purchase.

Specifications in this document are subject to change without notice. Check with UEI for current status.

### **Table of Contents**

| Chapter                                          | 1 Introduction                                                                                                                                                                   |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                              | Organization of This Manual1                                                                                                                                                     |

| 1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5 | DNx-429-516 Board Overview3Data Rate.3Guardian Diagnostic Support.3ARINC Transmitters.3ARINC Receivers.3Software Support.3                                                       |

| 1.3                                              | Features                                                                                                                                                                         |

| 1.4                                              | Indicators 4                                                                                                                                                                     |

| 1.5                                              | Specification                                                                                                                                                                    |

| 1.6                                              | Device Architecture                                                                                                                                                              |

| 1.7<br>1.7.1<br>1.7.2                            | ARINC-429 Word Format                                                                                                                                                            |

| 1.8<br>1.8.1<br>1.8.2<br>1.8.3<br>1.8.4          | Receiver Block11Receiver Block Components11RX FIFO12RX Filters12TX to RX Loopback Features13                                                                                     |

| 1.9<br>1.9.1<br>1.9.2<br>1.9.3                   | Transmitter Block14Hardware Sources for Transmit Data15Scheduler16TX FIFO25                                                                                                      |

| 1.10<br>1.10.1                                   | Wiring & Connections (pinout)       26         ARINC-429 Bus in Multi-drop Network       27                                                                                      |

| Chapter                                          | 2 Programming with the High-Level API                                                                                                                                            |

| 2.1                                              | About the High-level Framework                                                                                                                                                   |

| 2.2                                              | Creating a Session                                                                                                                                                               |

| 2.3                                              | Configuring the Resource String                                                                                                                                                  |

| 2.4                                              | Configuring the Timing                                                                                                                                                           |

| 2.5                                              | Reading Data                                                                                                                                                                     |

| 2.6                                              | Writing Data                                                                                                                                                                     |

| 2.7                                              | Programming the Output Scheduler                                                                                                                                                 |

| 2.8<br>2.8.1<br>2.8.2<br>2.8.3<br>2.8.4<br>2.8.5 | Scheduling Outputs Using Major/Minor Frames33Set MJ/MN Mode33Configure MJ/MN Frame Clock Rates34Add Scheduler Entries35Update Scheduler Table36Update Scheduler Using TX Pages36 |

| 2.9                                              | Programming the Label Filter                                                                                                                                                     |

#### DNx-429-516 ARINC 429 Board ii Table of Contents

| 2.10                               | Cleaning-up the Session                                                                                                                                                                                |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter                            | 3 Programming with the Low-Level API                                                                                                                                                                   |

| 3.1                                | About the Low-level API                                                                                                                                                                                |

| 3.2                                | Low-level Functions                                                                                                                                                                                    |

| 3.3<br>3.3.1                       | Low-level Programming Techniques.    41      Data Transfer Modes.    41                                                                                                                                |

| 3.4<br>3.4.1<br>3.4.2              | Configuring Board & Channels       42         Board Configuration       42         Channel Configuration       42                                                                                      |

| 3.5                                | Setting Modes of Operation 44                                                                                                                                                                          |

| 3.6                                | Setting the Baud Rate 46                                                                                                                                                                               |

| 3.7                                | Reading RX Data                                                                                                                                                                                        |

| 3.8<br>3.8.1<br>3.8.2              | Writing TX Data Using the FIFO       48         Configuring for FIFO Transmission       48         Configuring for FIFO Transmission with Delays       50                                              |

| 3.9<br>3.9.1<br>3.9.2<br>3.9.3     | Writing TX Data Using the Scheduler       52         Initializing the Scheduler Table       52         Programming Scheduler Timebase Values       52         Writing Scheduler Transmit Data       53 |

| 3.10<br>3.10.1<br>3.10.2<br>3.10.3 | Programming RX Filters       61         Filtering Messages Based on Labels       61         Filtering Messages Based on Parity       62         Filtering Messages Based on SDI       62               |

| Appendi                            | ix63                                                                                                                                                                                                   |

| A.1                                | Accessories                                                                                                                                                                                            |

### **List of Figures**

| Chapter     | 1 Introduction                                             | 1  |

|-------------|------------------------------------------------------------|----|

| 1-1         | The DNR-429-516 ARINC-429 Board                            | .4 |

| 1-2         | DNA/DNR-429-516 Logic Block Diagram                        |    |

| 1-3         | ARINC-429 Waveform Characteristics                         |    |

| 1-4         | General ARINC Word Format                                  |    |

| 1-5         | Receiver Diagram                                           |    |

| 1-6         | Transmitter Block Diagram                                  |    |

| 1-7         | Example of Programming the Scheduler in Default Operation  |    |

| 1-8<br>1-9  | Example of Programming the Scheduler in Frame Clock Mode   |    |

| 1-9<br>1-10 | Example Scheduler Table in Major/Minor Frame Mode          |    |

| 1-10        | DNx-429-516 Pinout Diagram                                 |    |

| 1-12        | Wiring for an ARINC-429 Network                            |    |

| Chapter     | 2 Programming with the High-Level API                      | 8  |

| Chapter     | 3 Programming with the Low-Level API                       | 9  |

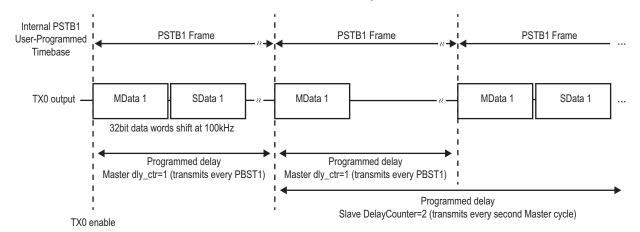

| 3-1         | Example of Transmit from TX FIFO in Delayed Mode5          | 51 |

| 3-2         | Example of Programming the Scheduler in Default Operation5 | 54 |

| 3-3         | Example of Programming the Scheduler in Frame Clock Mode5  | 7  |

| Append      | ix                                                         | 3  |

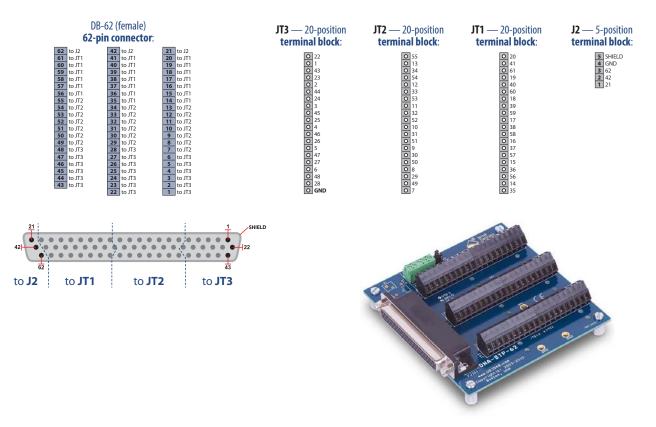

| A-1         | Pinout and Photo of DNA-STP-62 Screw Terminal Panel6       | 3  |

| Index       |                                                            | 4  |

### Chapter 1 Introduction

This document outlines the feature set and use of the DNx-429-516 ARINC-429 boards.

The DNx-429-516 is an ARINC-429 interface that provides 24 ARINC channels: 16 channels that can be individually configured as ARINC-429 transmitters or receivers plus an additional 8 dedicated ARINC-429 receiver channels.

**NOTE:** Note that the information in this manual is also applicable for the preliminary revision (p/n DNx-429-516-024).

This chapter contains the following sections:

- Organization of This Manual (Section 1.1)

- DNx-429-516 Board Overview (Section 1.2)

- Features (Section 1.3)

- Indicators (Section 1.4)

- Specification (Section 1.5)

- Device Architecture (Section 1.6)

- ARINC-429 Word Format (Section 1.7)

- Receiver Block (Section 1.8)

- Transmitter Block (Section 1.9)

- Wiring & Connections (pinout) (Section 1.10)

This DNx-429-516 User Manual is organized as follows:

1.1 Organization

#### of This Manual

#### Introduction

Chapter 1 provides an overview of the DNx-429-516 ARINC interface board features, device architecture, and connectivity.

- **Programming with the High-Level API** This chapter provides an overview of the how to create a session, configure the session, and format relevant data with the Framework API.

- **Programming with the Low-Level API** Chapter 3 describes low-level API commands for configuring and using the DNx-429-516 series board for serial operating modes.

- Appendix A Accessories This appendix provides a list of accessories available for use with the DNx-429-516 serial-line communication interface board.

- **Index** This is an alphabetical listing of the topics covered in this manual.

- **NOTE:** A glossary of terms used with the PowerDNA Cube/RACK and I/O boards can be viewed or downloaded from www.ueidaq.com.

#### **Manual Conventions**

To help you get the most out of this manual and our products, please note that we use the following conventions:

Tips are designed to highlight quick ways to get the job done or to reveal good ideas you might not discover on your own.

NOTE: Notes alert you to important information.

**CAUTION!** Caution advises you of precautions to take to avoid injury, data loss, and damage to your boards or a system crash.

Text formatted in **bold** typeface generally represents text that should be entered verbatim. For instance, it can represent a command, as in the following example: "You can instruct users how to run setup using a command such as **setup.exe**."

**Bold** typeface will also represent field or button names, as in "Click **Scan Network**."

Text formatted in fixed typeface generally represents source code or other text that should be entered verbatim into the source code, initialization, or other file.

#### Before you begin:

Before plugging any I/O connector into the Cube or RACK chassis, be sure to remove power from all field wiring. Failure to do so may cause severe damage to the equipment.

#### No HOT SWAP

Always turn POWER OFF before performing maintenance on a UEI system. Failure to observe this warning may result in damage to the equipment and possible injury to personnel.

#### Usage of Terms

Throughout this manual, the term "Cube" refers to either a PowerDNA Cube product or to a PowerDNR RACKtangle<sup>™</sup> rack mounted system, whichever is applicable. The term DNR is a specific reference to the RACKtangle, DNA to the PowerDNA I/O Cube, and DNx to refer to both.

| 1.2   | DNx-429-516<br>Board<br>Overview  | The DNx-429-516 board is an ARINC 429 communications interface for UEI's Cube and RACK chassis. The DNx-429-516 offers 16 channels that are individually configurable as transmitters or receivers and additionally 8 dedicated receiver channels.                                                                                                                                                                                                                    |

|-------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                   | The TX drivers on the TX/RX channels can be disabled on a channel-by-channel basis. To use a TX/RX channel as RX you do not enable the TX driver on that channel; enabling TX drivers is controlled via UEI API.                                                                                                                                                                                                                                                      |

| 1.2.1 | Data Rate                         | The boards comply with the ARINC-429 specification and run at either a high speed (100 kHz) or low speed (12.5 kHz) baud rate. Additionally, the channel speed can be set to frequencies other than 100 kHz and 12.5 kHz to support legacy devices. The speed is software-selectable on a per channel basis. To ensure data integrity, 256-word FIFOs are provided on every TX and RX channel.                                                                        |

| 1.2.2 | Guardian<br>Diagnostic<br>Support | DNx-429-516 boards are part of UEI's Guardian series, which equips the boards with additional test and diagnostic capabilities. Each transmit channel connects to an on-board ARINC-429 receiver, allowing data being transmitted on the 429 bus to be monitored using the on-board receivers.                                                                                                                                                                        |

| 1.2.3 | ARINC<br>Transmitters             | Channels may be set to transmit asynchronously or based on a hardware controlled scheduler. Each channel supports a transmission table that allows up to 256 unique schedules. Transmission schedule resolution is 100 µs.                                                                                                                                                                                                                                            |

|       |                                   | Asynchronous (non-scheduled) data may be sent with three priorities. High<br>priority data is sent immediately upon completion of the current transmission,<br>regardless of scheduled messages. Data sent with standard priority is<br>transmitted during times when no scheduled data is being sent. Finally, the<br>lowest priority is data streamed from a 256 word FIFO which is sent when no<br>scheduled, high or standard priority data is being transmitted. |

| 1.2.4 | ARINC<br>Receivers                | The DNx-429-516 series provides a variety of filtering capabilities. The board can be configured to only return data from specific labels. Data from up to 255 labels may be selectively read or the board can be set to read data from all labels.                                                                                                                                                                                                                   |

|       |                                   | A "new data only" filter can be enabled, which compares the received label data to the most recent previous reading and only returns data if something has changed.                                                                                                                                                                                                                                                                                                   |

|       |                                   | Data may also be filtered based on the SDI bits and parity errors.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.2.5 | Software<br>Support               | Software support for the DNx-429-516 is included with the board. Factory written and supported drivers are included for Linux and are available for other popular real-time operating systems including QNX and VxWorks.                                                                                                                                                                                                                                              |

|       |                                   | Users can develop applications using "low-level" C-based libraries or using the UEIDAQ Framework, which provides a comprehensive, easy to use API supporting all popular Windows programming languages. The UEIDAQ Framework supplies complete support for those creating applications in all popular data acquisition and control packages, including LabVIEW, MATLAB, as well as any application which supports ActiveX or OPC servers.                             |

#### **1.3 Features** DNx-429-516 features are listed below:

- 16 ARINC-429 individually configurable as TX or RX plus 8 dedicated RX channels (allowing for up to 24 RX channels)

- High Speed (100 kHz) or Low Speed (12.5 kHz) standard baud rate, selectable per channel; programmable custom rates from 10 kbaud to 200 kbaud

- Hardware Label filtering

- Hardware Transmit Scheduler (100 µS timing resolution)

- Automatic timestamping of data, software enabled/disabled

- Guardian Series Diagnostics, on-board 429 RXs allow read-back on each TX channel

- 350 V<sub>rms</sub> isolation between blocks of three channels and between chassis and channels

- Tested to withstand 5g Vibration, 50g Shock, -40 to +85°C Temperature, and Altitude up to 70,000 ft or 21,000 meters

- Weight of 104 g or 3.7 oz for DNA-429-516

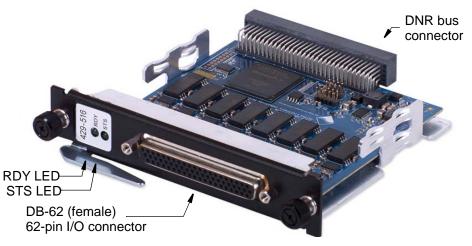

- **1.4 Indicators** The DNx-429-516 indicators are described in **Table 1-1** and illustrated in **Figure** 1-1.

| Table 1 | 1-1 429 | -516 In | dicators |

|---------|---------|---------|----------|

|---------|---------|---------|----------|

| LED Name | Description                                                                                                                                                         |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RDY      | Indicates board is powered up and operational                                                                                                                       |  |  |

| STS      | Indicates which mode the board is running in:                                                                                                                       |  |  |

|          | <ul> <li>OFF: Configuration mode, (e.g., configuring channels, running in point-by-point mode)</li> <li>ON: Operation mode, (e.g., running in VMap mode)</li> </ul> |  |  |

Figure 1-1 The DNR-429-516 ARINC-429 Board

#### **1.5 Specification** The technical specification for the DNx-429-516 is provided in the table below:

| Channel Configurations                                                                                                            |                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of channels                                                                                                                | 16 TX or RX and 8 dedicated RX channels                                                                                                                                                                                                                                                                      |

| ARINC Compliance                                                                                                                  | Fully compliant with ARINC 429                                                                                                                                                                                                                                                                               |

| Total RX loads                                                                                                                    | 20 per channel, 128 maximum per board                                                                                                                                                                                                                                                                        |

| Transmit Specifications                                                                                                           |                                                                                                                                                                                                                                                                                                              |

| Standard Data rate                                                                                                                | 100 kHz or 12.5 kHz selectable per channel                                                                                                                                                                                                                                                                   |

| Custom data rates                                                                                                                 | 10 kHz to 200 kHz for special applications                                                                                                                                                                                                                                                                   |

| FIFO size (TX or RX)                                                                                                              | 256 words                                                                                                                                                                                                                                                                                                    |

| Transmit modes                                                                                                                    | Scheduled or asynchronous. TX outputs may be disabled allowing a channel to be used as a Input.                                                                                                                                                                                                              |

| TX Scheduler specifications                                                                                                       |                                                                                                                                                                                                                                                                                                              |

| timing resolution                                                                                                                 | 100 microseconds                                                                                                                                                                                                                                                                                             |

| table size                                                                                                                        | Schedule up to 256 labels per channel                                                                                                                                                                                                                                                                        |

| Minor/Major Frames                                                                                                                | 16 Minor frames with double buffering of data array                                                                                                                                                                                                                                                          |

| Asynchronous TX modes                                                                                                             |                                                                                                                                                                                                                                                                                                              |

| High priority                                                                                                                     | transmit immediately upon completion of current transmission regardless of schedule                                                                                                                                                                                                                          |

| Standard priority                                                                                                                 | transmit when no scheduled data                                                                                                                                                                                                                                                                              |

| FIFO based                                                                                                                        | transmit when no scheduled, standard or high priority data is being sent                                                                                                                                                                                                                                     |

| Receive Specifications                                                                                                            |                                                                                                                                                                                                                                                                                                              |

| Standard Data rate                                                                                                                | 100 kHz or 12.5 kHz selectable per port                                                                                                                                                                                                                                                                      |

| Custom data rates                                                                                                                 | 10 kHz to 200 kHz for special applications                                                                                                                                                                                                                                                                   |

| FIFO size                                                                                                                         | up to 256 32-bit words, user selectable                                                                                                                                                                                                                                                                      |

| Receive filter size                                                                                                               | 1 to 255 Labels or disabled                                                                                                                                                                                                                                                                                  |

| SDI filter                                                                                                                        | enabled or disabled                                                                                                                                                                                                                                                                                          |

| New data only filter                                                                                                              | enabled or disabled by label or globally                                                                                                                                                                                                                                                                     |

| Parity checking                                                                                                                   | enabled or disabled                                                                                                                                                                                                                                                                                          |

| Date/Time stamping                                                                                                                | enabled or disabled by label or globally                                                                                                                                                                                                                                                                     |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                              |

| General Specifications                                                                                                            |                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                   | 350 Vrms. Isolation provided in channel pairs.<br>Channels 0-1, 2-3,14-15 share a common ground                                                                                                                                                                                                              |

| General Specifications                                                                                                            | 350 Vrms. Isolation provided in channel pairs.                                                                                                                                                                                                                                                               |

| General Specifications Isolation                                                                                                  | 350 Vrms. Isolation provided in channel pairs.<br>Channels 0-1, 2-3,14-15 share a common ground                                                                                                                                                                                                              |

| General Specifications<br>Isolation<br>Operating temperature<br>Vibration IEC 60068-2-6                                           | 350 Vrms. Isolation provided in channel pairs.<br>Channels 0-1, 2-3,14-15 share a common ground<br>tested -40 °C to +85 °C<br>5 g, 10-500 Hz, sinusoidal                                                                                                                                                     |

| General Specifications<br>Isolation<br>Operating temperature<br>Vibration IEC 60068-2-6<br>IEC 60068-2-64                         | 350 Vrms. Isolation provided in channel pairs.<br>Channels 0-1, 2-3,14-15 share a common ground<br>tested -40 °C to +85 °C<br>5 g, 10-500 Hz, sinusoidal<br>5 g (rms), 10-500 Hz, broad-band random<br>50 g, 3 ms half sine, 18 shocks @ 6 orientations                                                      |

| General Specifications<br>Isolation<br>Operating temperature<br>Vibration IEC 60068-2-6<br>IEC 60068-2-64<br>Shock IEC 60068-2-27 | 350 Vrms. Isolation provided in channel pairs.<br>Channels 0-1, 2-3,14-15 share a common ground<br>tested -40 °C to +85 °C<br>5 g, 10-500 Hz, sinusoidal<br>5 g (rms), 10-500 Hz, broad-band random<br>50 g, 3 ms half sine, 18 shocks @ 6 orientations<br>30 g, 11 ms half sine, 18 shocks @ 6 orientations |

Table 1-2 . DNx-429-516 Technical Specifications

**NOTE:** A DNx-429-516 transmitter can connect to 1 to 20 receiver(s) on one twisted pair, per ARINC-429 hardware specifications. However, note that due to power restrictions, the DNx-429-516 board can only drive a maximum of 128 receivers per board.

#### 1.6 Device Architecture

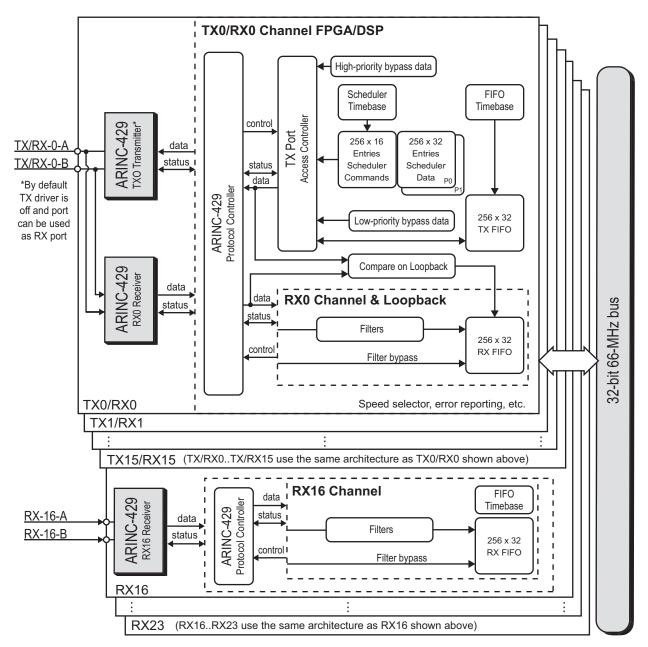

The DNx-429-516 board incorporates 24 parallel ARINC channels. Refer to **Figure 1-2** for block diagram.

Channels are grouped into 8 isolated blocks of 3 channels each: (TX0/RX0, TX1/RX1, RX16), (TX2/RX2, TX3/RX3, RX17), etc.

#### Figure 1-2 DNA/DNR-429-516 Logic Block Diagram

Each of the 16 TX/RX channels contains one ARINC transmitter and one receiver (channel 0..15). On power up, TX drivers are off, and the channel can be used as an ARINC receiver after enabled. If TX is enabled, the channel is set up to transmit messages and the receiver side of the channel can be used to loopback transmitted data for diagnostic purposes.

Additionally, the 429-516 provides 8 dedicated RX-only channels (RX16..RX23) that contain an ARINC receiver each.

The DNx-429-516 ARINC communication protocol functions are embedded into the FPGA. TX channels are driven by associated Holt HI-8596 line drivers. Dedicated RX channels use Holt HI-8455 receivers.

Channels are grouped into eight isolated blocks of 3 channels each:

- Block 0: TX0/RX0, TX1/RX1, RX16 •

- Block 1: TX2/RX2, TX3/RX3, RX17 •

- Block 2: TX4/RX4, TX5/RX5, RX18 •

- Block 3: TX6/RX6, TX7/RX7, RX19 .

- Block 4: TX8/RX8, TX9/RX9, RX20 •

- Block 5: TX10/RX10, TX11/RX11, RX21 •

- Block 6: TX12/RX12, TX13/RX13, RX22 •

- Block 7: TX14/RX14, TX15/RX15, RX23 •

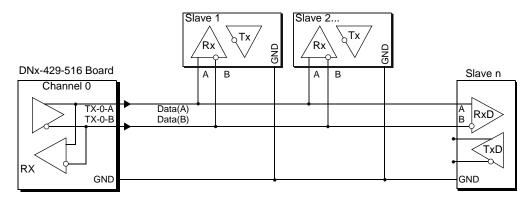

The transmission medium for an ARINC-429 bus is 78-ohm, twisted, shieldedpair cable, grounded at both ends and at any break in the cable shield. Each bus has only one transmitter, which can drive up to 20 external receivers.

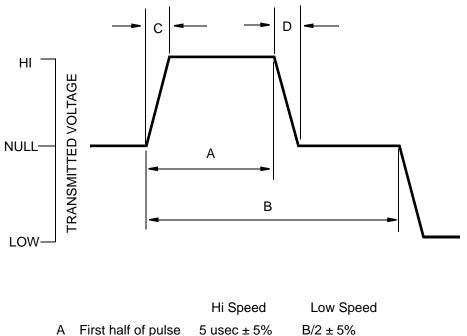

Waveform characteristics must conform to the specifications described in Figure 1-3.

| А | First half of pulse | 5 usec ± 5%   |

|---|---------------------|---------------|

| В | Full pulse cycle    | 10 usec ±2.5% |

- 1/bit rate ± 5% Full pulse cycle 10 usec ±2.5% 10 ± 5 usec Pulse Rise Time 1.5 ±0.5 usec

- 1.5 ±0.5 usec

- D Pulse Fall Time

- Received

С

February 2019

| Voltage | -              |

|---------|----------------|

| HI      | 6.5V to 13 V   |

| NULL    | -2.5V to +2.5V |

| LOW     | -6.5V to -13V  |

10 ± 5 usec

## 1.7 ARINC-429 Each ARINC-429 word is a 32-bit value containing 5 fields, as shown in Figure 1-4 and described in Table 1-3.

| 3 | 2     | 31 | 30 | 29    | 11                | 10 | 9  | 8     | 1 |

|---|-------|----|----|-------|-------------------|----|----|-------|---|

| F | P SSM |    | M  | DATA> | ← PAD ← DISCRETES | S  | DI | LABEL |   |

|   |       |    |    | MSB   | LSB               |    |    |       |   |

| Table 1-3 | Field Descri | ptions for | ARINC-429 | Words  |

|-----------|--------------|------------|-----------|--------|

|           |              |            |           | 110140 |

| Bit Values | Name   | Description                                                                                                                                                                                                                                                           |

|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32         | PARITY | PARITY is used to check the validity of the ARINC word.<br>Supported values are Odd, Even, and No Parity.<br>Refer to Section 1.7.1 for more information.                                                                                                             |

| 31:30      | SSM    | Sign/Status Matrix (SSM) indicates the status of data.                                                                                                                                                                                                                |

|            |        | Values for BCD data formats:                                                                                                                                                                                                                                          |

|            |        | <ul> <li>[11] Minus, South, West, Left, From, Below</li> <li>[10] TEST indicates data comes from a test source</li> <li>[01] NCD indicates data is missing because of non-hardware reason</li> <li>[00] Plus, North, East, Right, To, Above</li> </ul>                |

|            |        | Values for BNR data formats:                                                                                                                                                                                                                                          |

|            |        | <ul> <li>[11] OP indicates data is normal</li> <li>[10] TEST indicates data comes from a test source</li> <li>[01] NCD indicates data is missing because of non-hardware reason</li> <li>[00] FAIL indicates a hardware failure causing data to be missing</li> </ul> |

|            |        | See ARINC-429 protocol documentation for additional information regarding format details.                                                                                                                                                                             |

| 29:11      | DATA   | DATA contains 19 bits of data to transmit. Supported formats include bit-field, BCD, BNR, or mixed.                                                                                                                                                                   |

| 10:9       | SDI    | Source/Destination Identifiers (SDI) indicate the intended transmitter sending the data.                                                                                                                                                                              |

| 8:1        | LABEL  | LABEL identifies the data type. The Label is encoded in octal format and transmitted MSB first.                                                                                                                                                                       |

NOTE: Use of SDI and SSM is not mandatory.

Bits are transmitted on the ARINC bus in the following order.

8, 7, 6, 5, 4, 3, 2, 1, 9, 10, 11, 12 . . . 32

The Label (first 8 bits) is transmitted first, MSB first. After the label is sent, all other data fields are transmitted LSB first.

#### **1.7.1 Parity** Parity can be configured as Odd, Even, or No Parity.

#### For transmitters:

Selecting Odd or Even enables the DNx-429-516 transmitters to calculate parity and set the PARITY bit value in the outgoing word. When Odd or Even parity is selected, parity cannot be "forced" by the user.

- For TX Odd parity, the DNx-429-516 parity generator counts the number of 1s in bits 31..1 of the outgoing word. It auto-inserts bit 32 as a 1 or 0 to make the total number of ONES in the 32-bit ARINC word odd.

- For TX Even parity, the DNx-429-516 auto-inserts a 1 or 0 in bit 32 to make the total number of ONES even.

- When TX No Parity is selected, the DNx-429-516 outputs whatever bit 32 value is supplied by the user in the ARINC data word. This can be used for injecting parity errors by the user.

#### For receivers:

The DNx-429-516 receivers count the ONES in the received frame and calculate the value of the expected parity bit, according whether RX parity is programmed as Odd or Even.

The PARITY bit of the received message will be set as follows:

- For RX Odd parity, the 429-516 reports bit 32 (the parity bit) as

- 1 if there is a parity error (Even number of ONES in incoming word)

- 0 if the incoming word is correct (no parity error)

- For RX Even parity, the 429-516 reports bit 32 (the parity bit) as

- 1 if there is a parity error (Odd number of ONES in incoming word)

- 0 if the incoming word is correct (no parity error)

- When RX No Parity is selected, the 429-516 writes bit 32 as the actual PARITY bit that was received, regardless of parity errors.

The actual received parity bit (bit 32) is matched against the expected value; if the actual parity bit doesn't match the expected, a parity error is generated. Users have the option of programming the DNx-429-516 to ignore data from received frames with parity errors.

## **1.7.2DNx-429-516**The DNx-429-516 provides industry standard ARINC-429 protocol controllers to<br/>process data.

ARINC input data will need to be preformatted in a form that is common to protocol controllers, such as the Holt HI-3282 format (www.holtic.com).

When programming using the DNx-429-516 Framework, users provide Label, Data, SDI, SSM, and Parity fields and the Framework handles formatting (refer to **Chapter 2**). When programming using low-level API, functions are provided to handle formatting (refer to **Chapter 3**).

**Table 1-4** below provides a cross reference of Holt HI-3282 format,DNx-429-516 format, and ARINC-429 standard industry format.

Table 1-4. Cross Reference of Bit Numbering for Various Protocols

| Holt B<br>(compat<br>DNx-429- |      | DNx-429-516<br>Bit No. | ARINC<br>Standard<br>Bit No. | Name   | Description                                                                                |  |

|-------------------------------|------|------------------------|------------------------------|--------|--------------------------------------------------------------------------------------------|--|

| 15                            | Word | 31                     | 29                           | SIGN   | Sign bit for data                                                                          |  |

| 14-0                          | 2    | 30-16                  | 28-14                        | DATA   | 15 main data bits                                                                          |  |

| 15-13                         | Word | 15-13                  | 13-11                        | DATA   | 3 additional data bits                                                                     |  |

| 12-11                         | 1    | 12-11                  | 10-9                         | SDI    | Source/Destination Identifier (SDI). See<br>ARINC-429 protocol documentation for details   |  |

| 10-9                          |      | 10-9                   | 31-30                        | SSM    | Sign/Status Matrix (SSM) or data bits. See<br>ARINC-429 protocol documentation for details |  |

| 8                             |      | 8                      | 32                           | PARITY | Parity Bit. See Section 1.7.1 above for more information.                                  |  |

| 7                             |      | 7                      | 1                            | LABEL  | Label. Used to identify data types and                                                     |  |

| 6                             |      | 6                      | 2                            |        | associated parameters.                                                                     |  |

| 5                             |      | 5                      | 3                            |        | For RX ports, DNx-429 boards have a flexible                                               |  |

| 4                             |      | 4                      | 4                            |        | acceptance filter with an option to put only new                                           |  |

| 3                             |      | 3                      | 5                            | ]      | data into the RX FIFO or to trigger the                                                    |  |

| 2                             |      | 2                      | 6                            |        | Scheduler when the selected label is received.                                             |  |

| 1                             |      | 1                      | 7                            | 1      | When SDI bits are enabled, the Label Filter functions as a 10-bit identifier.              |  |

| 0                             |      | 0                      | 8                            | İ      |                                                                                            |  |

**NOTE:** The ARINC serial communication standard numbers bits from 32 (MSB) to 1 (LSB). The UEI DNx-429-516 numbers them from 31 to 0, and the Holt controllers use two 16-bit words with bits numbered from 15 to 0. Also note that only LABEL, PARITY, SSM, and SDI bits are strictly defined by the ARINC-429 standard. The rest of the bits may be used as a payload by various sub-protocols.

NOTE: Use of SDI and SSM is not mandatory.

Bits are transmitted on the ARINC bus in the following order.

8, 7, 6, 5, 4, 3, 2, 1, 9, 10, 11, 12 . . . 32

The Label (first 8 bits) is transmitted first, MSB first. After the label is sent, all other data fields are transmitted LSB first.

| 1.8   | Receiver                                                                                                                                                            | The DNx-429-516 provides the following ARINC receivers:                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       | Block                                                                                                                                                               | <ul> <li>16 ARINC receivers (RX0RX15) that share I/O pins with the 16 ARINC transmitters (TX0TX15)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|       |                                                                                                                                                                     | 8 dedicated ARINC receivers (RX16RX23)                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|       |                                                                                                                                                                     | RX0RX15 ports can receive ARINC messages from an external source or receive looped back messages from corresponding DNx-429-516 transmit channels (TX0TX15). When transmitters are enabled, transmit frames are looped back into the corresponding ARINC receiver for storage in the RX FIFO and/or comparison with the last transmitted frame. These receivers include additional comparators and diagnostic circuitry to provide loopback status and data read from transmitters. |  |  |

|       |                                                                                                                                                                     | RX16RX23 function as 8 ARINC receive-only ports.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 1.8.1 | Receiver                                                                                                                                                            | Each receiver block consists of the following components:                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|       | Block                                                                                                                                                               | 256-word RX FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|       | Components                                                                                                                                                          | <ul> <li>RX filters: Label acceptance filter, store new data only circuitry, parity<br/>error data rejection filter, SDI filtering enable/disable</li> </ul>                                                                                                                                                                                                                                                                                                                        |  |  |

|       |                                                                                                                                                                     | "Last received" data memory                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|       | ARINC-429 Receiver Hardware                                                                                                                                         | 255 entry<br>Label Acceptance<br>Filter<br>0x0 in the first entry<br>disables/bypasses filter.<br>0x0 in subsequent<br>entries skips them in<br>the verification/<br>acceptance process.<br>Raw Frame                                                                                                                                                                                                                                                                               |  |  |

|       | Timestamp Sourd<br>32-bit counter runr<br>from sub-divider fo<br>the 66 MHz clock,<br>shared across all F<br>channels. Resoluti<br>varies from 1 us to<br>1 second. | RX     RX Frame Counter (32-bit)       ion     Counts one of the following: all frames accepted by the                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Figure 1-5 Receiver Diagram

Figure 1-5 shows a block diagram of the ARINC receiver functionality.

As illustrated, received data is stored directly in the 256-word FIFO when filters are not enabled.

Filtering and timestamping can be enabled by choosing options when setting up the receiver mode.

Refer to **Chapter 2** for more information about programming using the high-level Framework API. Refer to **Chapter 3** for more information about using the low-level C-based API.

**1.8.2 RX FIFO** The RX FIFO can store up to 256 of the last received ARINC-429 32-bit frames, if timestamping is not selected. If timestamping is selected, the RX FIFO is limited to 128 frames and 128 timestamps. If filters are not selected, data is placed directly into the 256-word FIFO.

The timestamp source is a 32-bit counter running from a subdivider of the 66 MHz clock. Timestamps are shared across all channels.

- **1.8.3 RX Filters** The DNx-429-516 has the capability of accepting or rejecting incoming ARINC data frames on an individual port using any of the following features:

- Filtering Frames Based on Predefined Labels

- Filtering Frames with Parity Errors

- Filtering Frames Based on a Predefined SDI

- 1.8.3.1 Filtering Frames Based on Predefined Labels

Users can filter received frames based on a set of up to 255 labels that are userprogrammed into the Label Acceptance Filter table.

As an option, the receiver can additionally be programmed to accept only changed data. This option compares incoming ARINC frames with the last received frame and stores only changed frames into the RX FIFO. Unchanged

data is discarded.

**1.8.3.2** Filtering Frames with Parity Errors 429-516 hardware calculates the parity of each incoming ARINC word based on whether the channel is configured as even or odd parity. The actual received parity bit (bit 32) is matched against the expected value; if the actual parity bit doesn't match the expected, a parity error is generated.

Users have the option of rejecting incoming frames with parity errors and only storing frames with correct parity to the RX FIFO.

**1.8.3.3**Filtering<br/>Frames Based<br/>on a<br/>Predefined SDIUsers additionally have the option of filtering incoming frames based on the<br/>SDI field. When SDI filtering is enabled, users can specify a mask (SDIMASK)<br/>of the SDI value they wish to filter for and only messages with that SDI value will<br/>be stored in the RX FIFO.

## **1.8.4TX to RX**<br/>Loopback<br/>FeaturesHardware loopback through the DNx-429-516 RX0..RX15 receivers supports<br/>the same filtering options as receivers in non-loopback mode, as well as<br/>additional diagnostic features and status information.

For the RX0..RX15 receivers, hardware that compares the last TX frame with the looped-back RX frame provides an option to store the following data if the comparison fails:

- Expected TX frame

- Received RX frame

- Timestamp

- Error counters

- TX frame source, (e.g., Scheduler with entry number, TX FIFO, etc.) and error flags

The comparator may include or exclude the parity bit from the compare algorithm. This option ignores data with a bad parity bit setting.

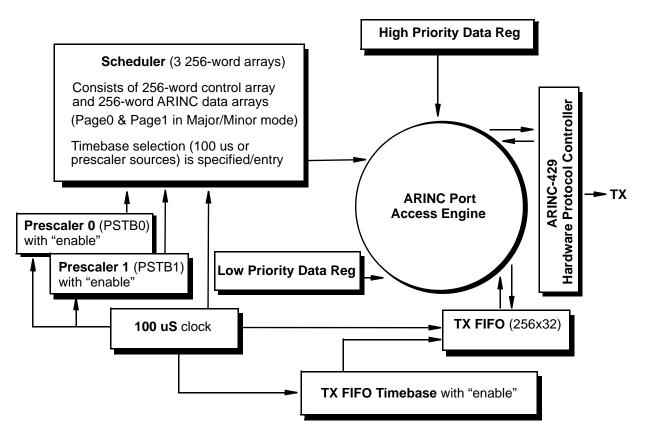

#### 1.9 Transmitter Block

Each transmitter port (TX0..TX15) is composed of the following hardware:

- sources for the data being transmitted

- scheduler and timebase hardware

- port access control state machine

- an ARINC-429 protocol controller

Users can write to four separate prioritized hardware sources to store data for transmission. Hardware sources for queuing transmit data include a high-priority data register, 256-word scheduler arrays, a low-priority data register, and a 256-word TX FIFO.

Data is passed to the ARINC protocol controller and transmitter hardware for transmission to externally designated receivers. Data can also be looped back to internal DNx-429-516 receivers as a diagnostic capability.

**NOTE:** Each transmit channel can be disabled for connection to redundant systems. Disabled transmit channels will be tristated when the board is powered up. When the board is powered down, transmit channels are grounded.

A block diagram of hardware sources for transmit data and timebase hardware is shown in **Figure 1-6**.

## 1.9.1 Hardware Transmitter data sources are assigned ARINC bus access according to the following priorities: Transmit Data Transmit Data

| Priority | Transmitter Source          | Description                                                                                                                                                                                                                                                            |  |

|----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Highest  | High-priority Data Register | The high-priority register transfers data immediately after the current TX operation is completed.                                                                                                                                                                     |  |

| Second   | Scheduler Data              | The Scheduler transfers data from a data array to the ARINC<br>bus based on the Scheduler mode configuration and also<br>based on the timing specified in the corresponding Scheduler<br>control word.                                                                 |  |

|          |                             | The 429-516 Scheduler supports the following operational modes:                                                                                                                                                                                                        |  |

|          |                             | Scheduler in Default operation                                                                                                                                                                                                                                         |  |

|          |                             | Scheduler in Frame Clock mode                                                                                                                                                                                                                                          |  |

|          |                             | Scheduler in Major/Minor Frame mode                                                                                                                                                                                                                                    |  |

|          |                             | Refer to Section 1.9.2 for more information.                                                                                                                                                                                                                           |  |

| Third    | Low-priority Data Register  | The low-priority register only transfers data when the data from the Scheduler and high-priority register are not available.                                                                                                                                           |  |

| Lowest   | TX FIFO                     | The 256-word output TX FIFO runs at the lowest priority and may output data in either of two modes:                                                                                                                                                                    |  |

|          |                             | <ul> <li>whenever the interface IC can accept data and none is<br/>available from the Scheduler</li> </ul>                                                                                                                                                             |  |

|          |                             | <ul> <li>on a "paced" mode, based on user-defined clock<br/>intervals</li> </ul>                                                                                                                                                                                       |  |

|          |                             | The TX FIFO is used by the Scheduler and priority data regis-<br>ters as temporary storage. The TX FIFO should be enabled for<br>all transmissions.<br>Additionally, the TX FIFO supports a delayed transmission<br>mode. Refer to Section 1.9.3 for more information. |  |

Table 1-5 Transmitter Source Priority

**NOTE:** The Scheduler and FIFO priorities may be swapped by setting a command bit using the DqAdv566SetMode() low-level API function.

Refer to Section 2.7 on page 32 for more information regarding programming using the high-level Framework API, and refer to **Chapter 3** for more information about low-level programming.

## **1.9.2 Scheduler** Each TX channel is equipped with a hardware Scheduler that can be programmed to send sequences of ARINC data words at a given rate without intervention of the host and/or software.

As a general rule, the Scheduler should be pre-programmed before enabling the ARINC transmitter; however, programming can be changed at any time during operation.

The 429-516 Scheduler supports the following operational modes:

| Scheduler Mode    | Description                                                                                                                                                                                                                                                                                                                                                    | Section         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

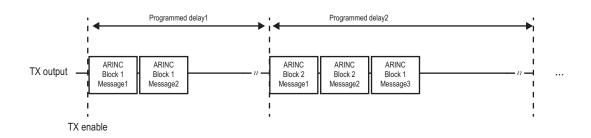

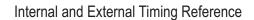

| Default Operation | Scheduling is based on master/slave word groupings. Master<br>control words are configured with a user-programmable delay<br>from the enabling of the TX channel, which is also the delay<br>between periodic master transmissions. Slave words always<br>directly follow master words.                                                                        | Section 1.9.2.2 |

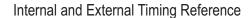

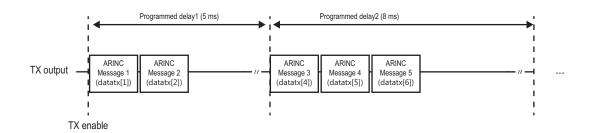

| Frame Clock       | Scheduling is based on master/slave word groupings. Master<br>control words are configured with a user-programmable delay<br>and frame repeat rates. Slave words can be scheduled on mul-<br>tiples of master word frames.                                                                                                                                     | Section 1.9.2.3 |

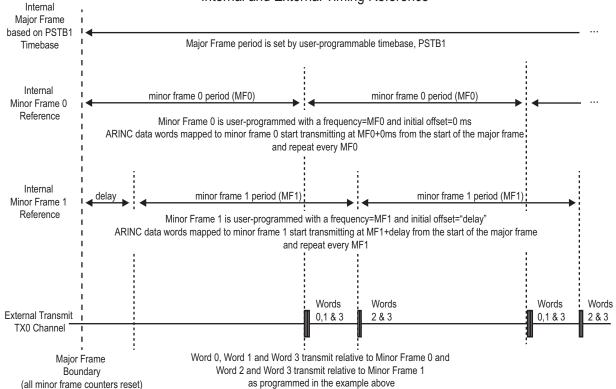

| Major/Minor Frame | <ul> <li>Scheduling is based on major/minor frames. A major frame clock triggers a sequence of minor frames, which are configured with user-programmable frame repeat rates and user-programmable time offsets relative to the start of a major frame.</li> <li>ARINC data is scheduled for transmission based on which minor frame it is mapped to</li> </ul> | Section 1.9.2.4 |

|                   | <ul> <li>the same data can be mapped to multiple minor<br/>frames</li> </ul>                                                                                                                                                                                                                                                                                   |                 |

Table 1-6 Summary of Scheduler Operational Modes

#### **1.9.2.1** Scheduler Hardware The Scheduler table consists of a control word array, which contains scheduling information and control flags, and a corresponding 256-word data array that contains the associated ARINC data to be transmitted.

When the Scheduler is in Major/Minor Frame mode, two data arrays are available, which provide two 256-word pages, Page0 and Page1, and allow data to be transmitted from one page while new data for transmit is written to the other page.

Each control word and corresponding data location are indexed as one entity (the control word with index 0 corresponds to the data location with the matching index).

Each scheduler entry can be enabled and disabled separately, and control and data arrays are read and write accessible. The control word, when read, also incorporates status bits, some of which are "sticky." To clear sticky status bits, the control entry must be re-written. Refer to **Table 1-7** for status bit descriptions.

Table 1-7 Scheduler Status Bit Descriptions

| Status Bit | Bit Name                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ECO        | Execution Complete Status Flag   | Indicates the scheduled entry has executed and was output<br>by the ARINC transmitter at least once. This is a sticky bit that<br>can be cleared only by writing a command to the Scheduler.                                                                                                                                                                                                                                                                                                                 |  |

| ME         | Marked for Execution Status Flag | <ul> <li>Indicates the following conditions:</li> <li>Set by the time scheduler when an entry is marked for execution (pending transmission)</li> <li>Cleared by the time scheduler for executed (transmitted) entries</li> </ul>                                                                                                                                                                                                                                                                            |  |

| EO         | Execution Overrun Status Flag    | Indicates that a periodic entry was scheduled for execution<br>while the ME bit was still set.<br>NOTE: If the EO bit is set, the data may be scheduled such<br>that the ARINC bus does not have enough capacity to transfer<br>it or that too much of the unscheduled data is pumped through<br>the transmit FIFO. This bit is a sticky bit that may be cleared<br>only by writing a command to the Scheduler. The EO bit also<br>triggers an "execution overrun" interrupt for the given trans-<br>mitter. |  |

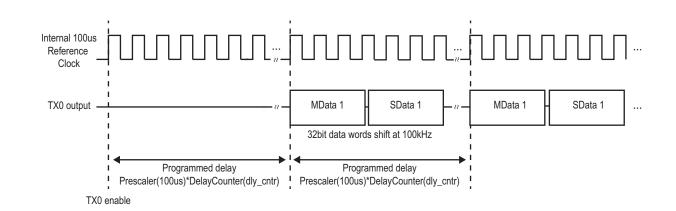

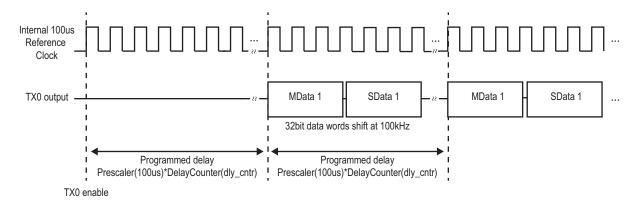

# 1.9.2.2Scheduler in<br/>DefaultIn Default operation, the scheduler array is written with a series of user-defined<br/>master/slave control words and corresponding ARINC transmit messages<br/>(data). The control word specifies the timing and master/slave groupings of the<br/>word(s) to be shifted out of the transmitter.

In Default operation, the slave words directly follow the master word. Scheduling is set by the master control word entry.

| Array Index | Scheduler Control Word                                                 | Scheduler Data Word (for TX)  |

|-------------|------------------------------------------------------------------------|-------------------------------|

| 0           | Master=TRUE; Periodic=TRUE;<br>Prescaler=100us; DelayCounter=dly_ctr   | Master Data Word:<br>MData 1  |

| 1           | Master=FALSE; Periodic=TRUE;<br>Prescaler=100us; DelayCounter=dly_cntr | Slave 1 Data Word:<br>SData 1 |

| 2           | NULL                                                                   | NULL                          |

| :           | :                                                                      | ÷                             |