# **DNR-ARINC-664**

#### 2-Channel ARINC-664 interface

- For use in RACKtangle® I/O chassis

- 2 independent or 1 dual-redundant channel

- 10/100/1000 Base-T implementation

- Transmit, Receive or Bus Monitor function

- Consecutive or user defined Sequence Numbers

- 10 µS time tags

- Error/Integrity checking

- Extensive filtering and traffic scheduling

DNR board only. For DNA, please contact uei.sales@ametek.com for availability.

# **GENERAL DESCRIPTION**

The DNR-ARINC-664 is a 2-channel ARINC 664 (including the Boeing EDE protocol) communications interface for UEI's RACKtangle I/O chassis. The board may be configured as two independent channels or one dual redundant channel. The network implementation fully supports 10, 100 and 1000 BASE-T speeds. The channels may operate as a receiver, transmitter or network/bus monitor. The DNR-ARINC-664 requires a single slot in the RACK.

In input mode, the user may time tag inputs with resolutions as low as 10 microseconds. The input automatically provides error/integrity checking, though this feature may be disabled if the application requires. Receive filtering is also supported based on the VL, Port and error detection.

The Monitor mode allows the user to capture all network traffic, or may be set with automatic filtering so only the desired information is captured. The Monitor mode will also gather a variety of statistics from the bus/network. If desired,

the monitor mode may be set to capture all UDP network traffic, regardless of whether it is configured based on the ARINC-664 protocol.

Transmit channels automatically configure traffic shape via Bandwidth Allocation Gaps (BAG) with 1, 2, 4, 8, 16, 32, 64 or 128 mS timing. Transmission may be based on an automatic scheduler, or in a oneshot asynchronous mode. Both Uni-cast and Multicast are fully supported. The transmitter will automatically generate consecutive Sequence Numbers. All transmission scheduled is done inhardware on-board.

The board is based on the Freescale 8347 processor running the DO-178 certified  $\mu$ C Operating System. In PowerDNA mode, the Cube/RACK itself also uses uC, so though the units are not certified to DO-178, the fact that the operating system already is will dramatically reduce certification time. Advanced users may also wish to implementspecial functions in the board's

1

firmware which can be implemented with custom µC code. Though the Cube/RACK is well supported with a variety of debugging tools a diagnostic RS-232 port is provided on the board allowing easy access to the lowest levels of the board's functionality. Software is included, providing a comprehensive, yet easy-to-use API that supports all popular operating systems, including Windows, Linux, and most realtime operating systems—such as QNX, Intime, VXworks, and more. Additionally, the UEIDAQ Framework—an even higher level Windows driver—supplies complete support for those creating applications in many popular Windows programming languages, as well as data acquisition software packages such as LabVIEW and MATLAB/Simulink.

# **TECHNICAL SPECIFICATIONS** (Typical at 25°C±5°C unless otherwise stated)

| Configuration              |                                                                                                    |

|----------------------------|----------------------------------------------------------------------------------------------------|

| Number of channels         | 2: supports A only, B only or dual redundant                                                       |

| Slots required             | Rquires one slot in the UEI RACKtangle                                                             |

| Ethernet BASE              | 10, 100 or 1000 BASE-T                                                                             |

| Channel functions          | Transmit, Receive or Monitor                                                                       |

| VLs supported              | Up to 2000 VLs or ports with up to 664 active                                                      |

| Underlying Processor       | Freescale 8347 running DO-178 certified OS                                                         |

| Receive Specifications     |                                                                                                    |

| Time tagging resolution    | 10 μS                                                                                              |

| Error/Integrity checking   | Integrity, Link-level, Sequence Number (SN)                                                        |

| Filtering                  | VL, Port and error detection filters                                                               |

| Monitor Specifications     |                                                                                                    |

| Configuration              | All or Filtered with or without time-tag                                                           |

| Error Checking             | Capture all, valid or invalid VLs                                                                  |

| Statistics Gathering       | Counters: PHY, Ethernet, IP, UDP, ARINC                                                            |

| Transmit Specifications    |                                                                                                    |

| Traffic shape via BAG      | 1, 2, 4, 8, 16, 32, 64 or 128 mS                                                                   |

| Transmission scheduling    | 10 μS resolution schedule scheduling of VLs and ports. All scheduling is done in hardware.         |

| Transmission configuration | Unicast and multicast addressing                                                                   |

| Sequence Numbers           | Auto-Sequenced Consecutive                                                                         |

| General Specifications     |                                                                                                    |

| Debugging options          | Via Cube/RACKtangle chassis backplane or directly to board via RS-232 port.                        |

| Loop back testing          | Loop back mode on the DNx-ARINC-664 allows automatic self-test                                     |

| Operating temperature      | Tested -40 °C to +85 °C                                                                            |

| Vibration                  |                                                                                                    |

| IEC 60068-2-6              | 5 g, 10–500 Hz, sinusoidal                                                                         |

| IEC 60068-2-6              | 5 g (rms), 10–500 Hz, broad-band random                                                            |

| Shock— (IEC 60068-2-27)    | 100 g, 3 ms half sine, 18 shocks @ 6 orientation 30 g, 11 ms half sine, 18 shocks @ 6 orientations |

| Humidity                   | 5 to 95%, non-condensing                                                                           |

| Altititude                 | 120,000 ft                                                                                         |

| Power consumption          | 6 Watts, maximum                                                                                   |

| MTBF                       | 130,000                                                                                            |

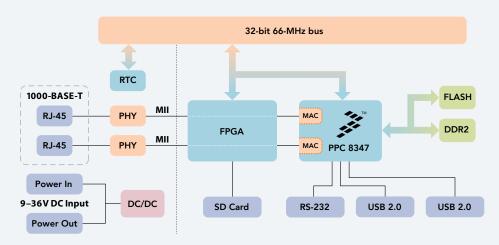

## **ANALOG INPUT BLOCK DIAGRAM**

## **ORDERING INFORMATION**

| Part Number       | Description                                                                             |

|-------------------|-----------------------------------------------------------------------------------------|

| DNR-ARINC-664     | Dual channel ARINC-664 interface for DNR series RACKtangle chassis. (Requires one slot) |

| Extended Warranty | Option to purchase UEI's extended 10 year warranty is available                         |