# DNA-DIO-401 for use with "Cube" I/O chassis DNR-DIO-401 for use with "Cube" I/O chassis DNR-DIO-401 for use with RACKtangle™ I/O chassis A digital input channels Supports wide range of digital logic levels User-programmable hysteresis I/O throughput rate of 1KS/sec Requires external 7-36V (24V nominal) power source

Supports UEIDaq Framework Data Acquisition Software Library for Windows. Linux and QNX drivers available. Visit our website for more details

# **General Description:**

The DNA/DNR-DIO-401 are digital input boards designed for low-speed, high-reliability isolated industrial digital I/O. The DNA-DIO-401 is compatible with UEI's "Cube" chassis while the DNR-DIO-401 is designed for installation in the RACKtangle I/O chassis.

The DNA/DNR-DIO-401 features 24 digital input channels, I/O throughput rate of 1kHz, and offers 350Vrms isolation between layers. The board is compatible with 5-36V digital logic levels and can accept a wide range of user-supplied power sources (7 to 36V DC). In Cube based applications, the DNA-DIO-401 can be powered internally using a DNA-PC-912 power conversion layer. When a single DNA-PC-912 is used to power multiple DNA-DIO layers, total power consumption should not exceed 40W. Digital inputs on the DNA-DIO-401 use a unique programmable hysteresis feature which dramatically improves noise immunity of input signals. All digital inputs are protected with a 100mA PTC fuse and ESD/overvoltage protection device.

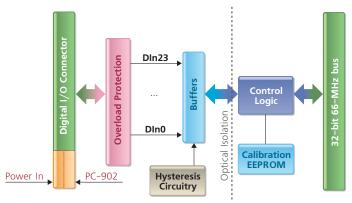

## **Block Diagram:**

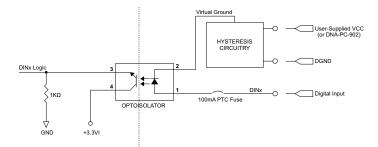

# **Simplified Input Channel Diagram**

# **Technical Specifications:**

| recurrent oper incurrons.                       |                                              |       |       |       |  |  |

|-------------------------------------------------|----------------------------------------------|-------|-------|-------|--|--|

| Number of channels                              | 24 digital inputs                            |       |       |       |  |  |

| Logic Level                                     | 5V - VCC                                     |       |       |       |  |  |

| Input FIFO                                      | 1024 samples                                 |       |       |       |  |  |

| Default Hysteresis Values                       | Lower DAC limit: 200<br>Upper DAC limit: 300 |       |       |       |  |  |

| Input High Voltage:                             | @7V                                          | @12V  | @24V  | @36V  |  |  |

| (with default hysteresis)                       | 4.5V                                         | 4.75V | 10.5V | 13V   |  |  |

| Input Low Voltage:<br>(with default hysteresis) | @7V                                          | @12V  | @24V  | @36V  |  |  |

|                                                 | 4.25V                                        | 4V    | 6.75V | 8.75V |  |  |

| Input Protection                                | ±40V over/under voltage, 7kV ESD             |       |       |       |  |  |

| Internal Sampling Rate                          | 2 kHz                                        |       |       |       |  |  |

| I/O Throughput Rate                             | 1 kHz max                                    |       |       |       |  |  |

| Power Requirements (VCC)                        | 7-36V (24V nominal) - external source        |       |       |       |  |  |

|                                                 | or DNA-PC-912 internally                     |       |       |       |  |  |

| Power Consumption                               | @7V                                          | @12V  | @24V  | @36V  |  |  |

|                                                 | 0.5W                                         | 0.6W  | 0.8W  | 1.6W  |  |  |

| Physical Dimensions                             | 3.875" x 3.875" (98 x 98 mm)                 |       |       |       |  |  |

| Operating Temp. Range                           | Tested -40 to +85 °C                         |       |       |       |  |  |

| Operating Humidity                              | 0 - 95%, non-condensing                      |       |       |       |  |  |

| Isolation                                       | 350Vrms                                      |       |       |       |  |  |

|                                                 |                                              |       |       |       |  |  |

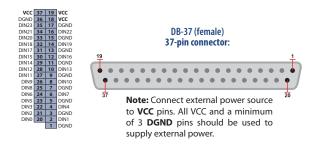

# **Pinout Diagram:**

## **Connection Options:**

| Cable                | Screw Terminal Panel | Description                                         |                       |  |

|----------------------|----------------------|-----------------------------------------------------|-----------------------|--|

| DNA-CBL-37S          | DNA-STP-37           | Shielded cable connection to 37-way terminal panel. |                       |  |

| DNA-CBL-37           | DNA-STP-37           | Ribbon cable connection to 37-way terminal panel.   |                       |  |

| United Electropic In | dustrios las         | 1                                                   | http://www.upidag.com |  |

United Electronic Industries, Inc. Tel: **(508) 921-4600**

Hysteresis Setup: Hysteresis is a very powerful feature that improves noise immunity on the digital inputs in industrial environments. Hysteresis on the DNA-DIO-401 is implemented as follows:

Two user programmable digital-to-analog converters are used to set upper and lower limits for the hysteresis function. These D/A converters are referred to as Lower limit DAC and Upper limit DAC. DAC outputs are connected to the multiplexer and then amplified using the high-speed amplifier. The amplifier drives the 'virtual' ground of the optical isolator.

- All inputs initially read while optical isolators are driven with virtual ground level that corresponds to the value of Lower DAC

- Another read is performed while the optical isolators are driven with a virtual ground level that corresponds to the value of Upper limit DAC

- If digital input values from both reads are the same the input signal state is assigned to the last read value, otherwise input signal state is unchanged

- This process repeats itself 1000 times a second

To set the hysteresis values, program the Lower and Upper DACs with an arbitrary number from 0 to 1023. The value of the Upper DAC should always be greater than LowerDAC by at least 50. Actual DAC values should be selected based on user requirements using the formula below:

$DAC Value^{3} = \frac{Desired Hysteresis Voltage}{VCC \times 800}$

$^3$  Since different optocouplers have different characteristics, this formula gives you approx  $\pm 10\%$  accuracy.