# **DNA/DNR-PL-820**

### **Programmable FPGA board**

- DNA-PL-820 for use in "CUBE" chassis

- DNR-PL-820 for RACKtangle<sup>™</sup> I/O chassis

- · Ideal for development of custom high speed controllers

- MAX 10 FPGA with 50k usable logic elements

- 1638 kB usable embedded memory,

- 144 embedded multipliers

- 4 internal PLLs for timing/clock generation

- Instant-on functionality

- · Uses standard Altera Quartus II toolkit

- Reprogrammable in-system with UEI software or through external JTAG connection

- DB62 I/O connectors

10-Year Availability Guarantee

1

DNA-PL-820 shown.

There is a mimumum quantity purchase on the DNx-PL-820. Please call us for details.

## **General Description:**

The DNA-PL-820 and DNR-PL-820 are user programmable FPGA boards compatible with UEI's popular Cube and RACKtangle chassis respectively. The board allows an FPGA programmer to add custom FPGA functionality to the DNx family and the various platforms it supports. The DNA/DNR versions are electronically identical and differ only in the mechanical features required for installation in the RACKtangle or Cube.

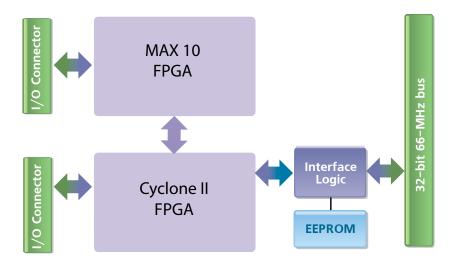

The DNx-PL-820 is a two board, base/daughter card product. The bottom board (left in a DNR RACK) includes a Cyclone II FPGA while the upper board (right in the RACK) provides a MAX 10 FPGA. The Cyclone board is used exclusively as the interface between the DNx bus and the MAX 10 FPGA chip. The MAX 10 chip is fully programmable by the user using popular Altera development tools, including the embedded Nios II processor.

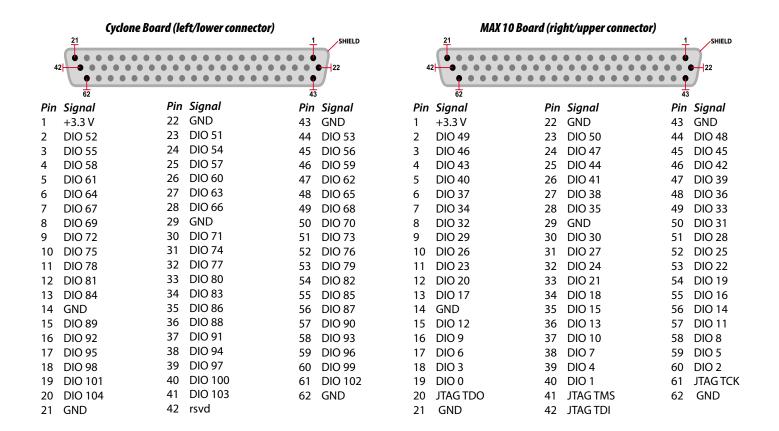

The MAX 10 board allows user developed FPGA applications to be installed and run on the board. 104 GPIO pins are brought out from the MAX 10 FPGA and are available for connections to user I/O. 51 bits are provided on the Cyclone board's I/O connector while 53 are provided on the MAX 10 board connector.

The MAX 10 has a variety of unique and powerful features that make it an ideal choice as a custom FPGA target. Included in these features is a unique, instant-on capability that allows the MAX 10 application to begin running immediately, without regard to whether the Cube or RACKtangle has completed its boot-up process. The MAX 10 also supports user and dual configuration FLASH, DSP blocks and Nios II embedded processor functionality.

The MAX 10 chip may be programmed by a JTAG interface that is brought out to the I/O connector or by the DNA backplane (via the Cyclone chip)by a utility provided by UEI. A set of jumpers on the board allows the JTAG interface to be disabled when security concerns mandates it. Security is further provided by the MAX 10's implementation of a nonvolatile security key. Without the key the MAX 10's FPGA image cannot be read or written.

The unit is shipped with an FPGA Image installed in the MAX 10 that simply sets each I/O pin as a general purpose DIO pin. The UEI API can then set each I/O bit independently as input or output. The PL-820 includes a test adaptor that connects the I/O pins from the Cyclone II board's I/O connector to the MAX 10 board's I/O connector (recall all GPIO pins are connected to the MAX 10). This allows each I/O pin to be exercised as both input and output and allows a quick self-test to ensure all I/O pins are fully functional

# **Technical Specifications:**

| le .                     | D.1.4                                             |

|--------------------------|---------------------------------------------------|

| Formats                  | DNA-series for "Cube" chassis                     |

|                          | DNR-series for RACKtangle chassis                 |

| FPGA type                | MAX 10, 10M50DCF484 series                        |

| Clock Frequency          | two programmabe clocks,up to 33 MHz,              |

|                          | provided by Cyclone II chip                       |

| FPGA Cells available     | up to 50,000                                      |

| Available block memory   | up to 1,638 kiloByte                              |

| Embedded multipliers     | 144 (18 x 18)                                     |

| PLLs available           | 4                                                 |

| User Flash memory        | up to 736 kByte                                   |

| A/D converters           | 2 plus one internal temp sensor                   |

| I/O connectors           | 62-pin "D" (female DB62)                          |

| I/O configuration        | Cube: Requires two consecutive slots              |

|                          | RACK: Requires mounting in slot 12                |

| Power consumption        | 5.0 W not including power sourced to              |

|                          | external circuitry                                |

| Operating temp. (tested) | -40°C to +85°C                                    |

| Operating humidity       | 95%, non-condensing                               |

| Vibration IEC 60068-2-6  | 5 g, 10-500 Hz, sinusoidal                        |

| IEC 60068-2-64           | 5 g (rms), 10-500Hz, broadband random             |

| Shock IEC 60068-2-27     | 50 g, 3 ms half sine, 18 shocks @ 6 orientations  |

|                          | 30 g, 11 ms half sine, 18 shocks @ 6 orientations |

| MTBF                     | 500,000 hours                                     |

|                          |                                                   |

The Cyclone chip communications with the MAX 10 utilizing two, fully programmable SPI interfaces. An fixed SSI interface is also included but it is currently reserved for system level configuration purposes. The Cyclone chip also provides two programmable clock signals to the MAX 10.

Unlike most DNx series boards, the DNx-PL-820 is not isolated from the DNx chassis. However, all I/O pins are protected with 165 Ohm series resistors and low capacitance bidirectional protection diodes.

Software for the DNx-PL-820 includes a high level, easy to use interface that allows you to configure and use the two SPI ports that connect the Cyclone and MAX 10 chips. It also allow you to program the MAX 10 chip from your host PC through the Cube/RACK's Ethernet port. Finally the software provided allows you to control/monitor all the GPIO included on the Cyclone II board (and the MAX 10 in its default state). The API provided is compatible with Windows, Linux, VxWorks, QNX and more.

### **Block Diagram:**

#### **Pinout:** (62-pin female dSub connectors)

United Electronic Industries, Inc. Tel: **(508) 921-4600**