# PD2-A0-16/16

## 16-Channel PCI Card for Analog Output Data Acquisition

- 16 analog outputs (16-bit resolution)

- 8 digital inputs; 8 digital outputs

- Three 24-bit counters/timers

- Three clock/interrupt lines

- · Channel list (64 locations)

- · Independent waveform on each channel

- · Simultaneous channel update; update on external event

- 2k samples onboard buffer size (upgradable to 64k samples)

Supports UEIDaq Framework Data Acquisition Software Library for Windows. Linux and QNX drivers available. Visit our website for more details.

#### **General Description:**

**Technical Specifications:**

Offering 16 analog outputs with 16-bit resolution, the PD2-AO-16/16 PCI-bus data acquisition board expands on the dual 12-bit calibration DAC-based output supplied on PD2-MF multifunction boards. Here you not only significantly increase the number of analog outputs, you also keep 16 digital I/O lines and three counter/timers. With these functions, the PD2-AO-16/16 is well suited to implement complex closed-loop systems as well as handle motor control and many other industrial-automation tasks.

The card calibrates each analog output individually without using trimpots. Instead relies on a special D/A based scheme that stores calibration coefficients in EEPROM and loads them automatically upon power up. This method also keeps board outputs in a predefined user-programmable state upon system startup.

| Analog Outputs          |                                       |  |

|-------------------------|---------------------------------------|--|

| Number of channels      | 16                                    |  |

| Resolution              | 16 bits                               |  |

| Update rate             | 100 kS/s per channel;                 |  |

|                         | 450kS/s aggregate in non-DMA mode;    |  |

|                         | up to 1100 kS/s aggregate in DMA mode |  |

| DSP buffer size         | 2k samples (2 buffers x 1k sample)    |  |

| Type of D/A             | double-buffered                       |  |

| Data transfer modes     | DMA, interrupt, software              |  |

| Accuracy                | ±3 LSB max                            |  |

| DNL                     | ±3 LSB max                            |  |

| Monotonicity over temp. | 15 bits, -40 to 85°C                  |  |

| Calibrated gain error   | 3mV typ, 6mV max @ ±9.8V              |  |

| Calibrated offset error | 1mV typ, 2mV max @ 0.0V               |  |

| Output range            | ±10V (custom ranges available)        |  |

| Output coupling         | DC                                    |  |

| Output impedance        | 0.15Ω max                             |  |

| Current drive           | ±20 mA min                            |  |

| Capacitive loads        | 180 pF min                            |  |

| Settling time           | 10μs to 0.003%                        |  |

| Slew rate               | 10V/μs                                |  |

| Gain bandwidth          | 1 MHz                                 |  |

| Noise                   | less than 2 LSB RMS, 0-10000 Hz       |  |

short to ground, ±15V 0.0000V ±5mV (default),

user programmable

25 ppm/°C

| Digital I/O         |                                          |  |  |

|---------------------|------------------------------------------|--|--|

| Number of channels  | 8 inputs, 8 outputs                      |  |  |

| Compatibility       | CMOS/TTL, 2kV ESD protected              |  |  |

| Power-on state      | logic zero (default),                    |  |  |

|                     | user programmable                        |  |  |

| Data transfer modes | DMA, interrupt, software                 |  |  |

| Input termination   | 4.7kΩ pull-up to 5V                      |  |  |

| Output high level   | 3.0V typ @ -32mA, 3.4V typ @ -16mA, 4.2V |  |  |

|                     | @ -2mA                                   |  |  |

| Output low level    | 0.55V max @ 64mA                         |  |  |

| Input low voltage   | 0.0 - 0.8V                               |  |  |

| Input high voltage  | 2.0 - 5.0V                               |  |  |

| Counter/Timer       |                                          |  |  |

| Number of channels  | 3                                        |  |  |

| Resolution          | 24 bits                                  |  |  |

| Max frequency       | 16.5 MS/s for external clock,            |  |  |

|                     | 33 MS/s for internal DSP clock           |  |  |

| Min frequency       | 0.00002 Hz for internal clock,           |  |  |

|                     | no low limit for external clock          |  |  |

| Min pulse width     | 20 ns                                    |  |  |

| Output high level   | 2.9V typ @ -4 mA                         |  |  |

| Output low level    | 0.5V min @ 4 mA                          |  |  |

| Protection          | 7 kV ESD, ±30V over/undershoot           |  |  |

| Input low voltage   | 0.0 - 0.8V                               |  |  |

| Input high voltage  | 2.0 - 5.0V                               |  |  |

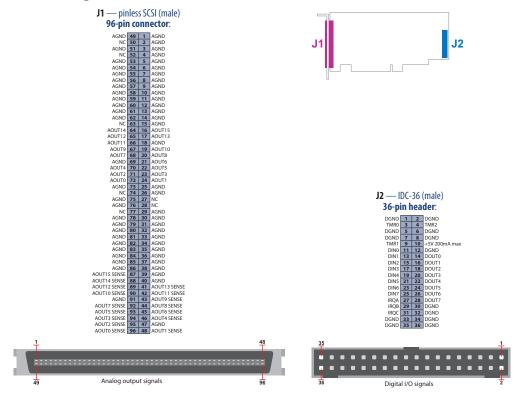

#### **Connection Schemes:**

Output protection

Power-on state

Gain drift

| Connector<br>On The Board | Cable<br>Required | Target<br>Panel  | Description                                                                         |

|---------------------------|-------------------|------------------|-------------------------------------------------------------------------------------|

| J1                        | PD-CBL-96         | PD2-AO-STP-16    | Carries analog output lines to 16-channel terminal panel                            |

| J2                        | PD-CBL-37         | PD2-AO-STP-16    | Carries 8 digital input and 8 digital output lines to 16-channel terminal panel     |

| J1                        | PD-CBL-96         | PD-BNC-64*       | Carries analog output lines to 64-channel BNC terminal panel                        |

| J2                        | PD-CBL-37         | PD-BNC-64        | Carries 8 digital input and 8 digital output lines to 64-channel BNC terminal panel |

| J2                        | PD-CBL-3650-8/8   | PD2-DIO-BPLANE16 | Carries digital lines to digital isolation panel for adding relays to the DIO lines |

| J1                        | PD-CBL-96         | PD-AO-AMP-100    | Amplifies analog outputs to ±100V per channel                                       |

| J1                        | PD-CBL-96         | PD-AO-AMP-115    | Amplifies analog outputs to ±115V per channel                                       |

<sup>\*</sup>PD-BNC-64 was initially designed for analog input subsytem of UEI's multifunction boards. Thus the analog output signals transfered via PD-CBL-96 will not match the signal designations on PD-BNC-64's J1 connector. See PowerDAQ Analog Output Manual for more details and remapping diagram.

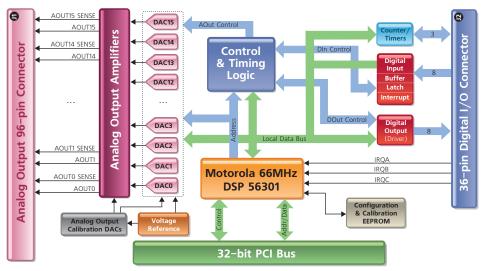

## **Block Diagram:**

Note: AOUTX on PD2-AO-16/16 board is internally connected to the corresponding AOUTX SENSE line. If you need remote sensing option, please use PD2-AO-32/16HC board.

### **Pinout Diagrams:**