## MD#**UEI-MD-402-R20000610**

Document type : Datasheet

# UEI-817 Datasheet

# Date 06.10.2000 UEI P/N UEI-817 Revision A and I

The information below is a general specification update for the UEI-817 boards.

#### DIGITAL I/O FEATURES

- RTI-817 drop-in replacement

- Three 8-bit ports

- Each port can be independently configured as input or output(\*)

- External/internal data latch for the each port

- IRQ on digital input change for the port 0

- Read-back feature for the output

- Digital input change auto-latch for the port 0

- Occupies one ISA slot

#### SPECIFICATIONS

|               | Features                    | Specification                                                            |  |  |  |

|---------------|-----------------------------|--------------------------------------------------------------------------|--|--|--|

| Digital I/O   | Number of channels          | 24 channels, selectable in 8-bit ports as inputs                         |  |  |  |

|               |                             | or outputs (output polarity is inverted for solid-                       |  |  |  |

|               |                             | state relay compatibility)                                               |  |  |  |

|               | I/O type                    | TTL                                                                      |  |  |  |

|               | Input Signal Levels         | I⊾= -10 uA maximum                                                       |  |  |  |

|               |                             | l⊩= 10 uA maximum                                                        |  |  |  |

|               |                             | V⊫= 0.8 V maximum                                                        |  |  |  |

|               |                             | VIII = 2.0 V minimum                                                     |  |  |  |

|               | Output Signal Levels        | lo∟= 24 mA maximum                                                       |  |  |  |

|               |                             | loн = -3.2 mA maximum                                                    |  |  |  |

|               |                             | Vo∟= 0.5 V maximum                                                       |  |  |  |

|               |                             | Vон = 2.4 V minimum; 3.6 V typical; 4.6V                                 |  |  |  |

|               |                             | maximum                                                                  |  |  |  |

|               | Maximum Input Voltage       | 7V                                                                       |  |  |  |

|               | Isolation                   | none                                                                     |  |  |  |

|               | Static Discharge Voltage    | 2000 V                                                                   |  |  |  |

|               | Output Supply Current       | 250 mA                                                                   |  |  |  |

|               | Setup Time                  | 10 ns                                                                    |  |  |  |

|               | Hold Time                   | 10 ns                                                                    |  |  |  |

|               | External Latch Pulse        | 10 ns                                                                    |  |  |  |

| System        | Base Address                | 4 consecutive byte addresses in the I/O address<br>space, DIP selectable |  |  |  |

| Connectors/   | DIO J1 Connector            | 50-pin male IDC header                                                   |  |  |  |

| Dimensions    | Dimensions                  | 4.2"x3.63"                                                               |  |  |  |

| Environmental | Operating Temperature Range | 070 deg C                                                                |  |  |  |

|               | Storage Temperature Range   | -2585 deg C                                                              |  |  |  |

|               | Relative Humidity           | 090% (non-condensing)                                                    |  |  |  |

| Power         | Power Consumption           | +5VDC 0.5A                                                               |  |  |  |

|               | J1 +5V power fuse           | 250 mA poly-switch resetable fuse                                        |  |  |  |

The table below is a specification for the UEI-817 board:

#### CONFIGURING THE UEI-817

Following items are configurable on the UEI-817

- I/O address

- Input/output mode for the each port

- Interrupt request line selection

- Input latch selection

- Input change-of-state latch for the port 0

The table below shows factory configuration of the UEI-817 board:

| Selection      | Factory Configuration           | Jumper settings                 |

|----------------|---------------------------------|---------------------------------|

| I/O Address    | 300h                            | S1 DIP switch : 1-6 ON, 7-8 OFF |

| I/O mode       | Ports 0-2 set as outputs        | W6 AB, W7 AB, W8 AB             |

| Input change-  | Port 0 is set to normal         | W4 BC                           |

| of-state latch | operation – input data is       |                                 |

|                | latched by the read data signal |                                 |

|                | from the host PC                |                                 |

| Interrupt      | IRQ2                            | W9 MN                           |

| Request Line   |                                 |                                 |

| Input Latch    | Normal operation – port 0-2     | W1 BC, W2 BC, W3 BC             |

| Signal Source  | input data is latched by the    |                                 |

|                | read data signal from the host  |                                 |

|                | PC                              |                                 |

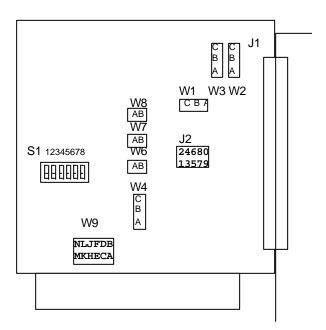

#### **UEI-817** Jumper locations

#### I/O Address selection

I/O address configuration is required to select a location for the UEI-817's 4-byte I/O address map in the PC I/O space. A factory default setting is 300h. To select an alternative I/O address use DIP switch S1. This switch contains eight switches. See table below for the address selection settings:

| DIP Switch selection |     |     |     |     |     |     | Hex I/O<br>Address |        |

|----------------------|-----|-----|-----|-----|-----|-----|--------------------|--------|

| 1                    | 2   | 3   | 4   | 5   | 6   | 7   | 8                  |        |

| -                    | -   | -   | -   | -   | -   | ON  | OFF                | 2xx    |

| -                    | -   | -   | -   | -   | -   | OFF | OFF                | 3xx    |

| -                    | -   | ON  | ON  | ON  | ON  | -   | -                  | x0x    |

| -                    | -   | OFF | ON  | ON  | ON  | -   | -                  | x1x    |

| -                    | -   | ON  | OFF | ON  | ON  | -   | -                  | x2x    |

| -                    | -   | OFF | OFF | ON  | ON  | -   | -                  | хЗх    |

| -                    | -   | ON  | ON  | OFF | ON  | -   | -                  | x4x    |

| -                    | -   | OFF | ON  | OFF | ON  | -   | -                  | x5x    |

| -                    | -   | ON  | OFF | OFF | ON  | -   | -                  | x6x    |

| -                    | -   | OFF | OFF | OFF | ON  | -   | -                  | x7x    |

| -                    | -   | ON  | ON  | ON  | OFF | -   | -                  | x8x    |

| -                    | -   | OFF | ON  | ON  | OFF | -   | -                  | x9x    |

| -                    | -   | ON  | OFF | ON  | OFF | -   | -                  | xAx    |

| -                    | -   | OFF | OFF | ON  | OFF | -   | -                  | xBx    |

| -                    | -   | ON  | ON  | OFF | OFF | -   | -                  | xCx    |

| -                    | -   | OFF | ON  | OFF | OFF | -   | -                  | xDx    |

| -                    | -   | ON  | OFF | OFF | OFF | -   | -                  | xEx    |

| -                    | -   | OFF | OFF | OFF | OFF | -   | -                  | xFx    |

| ON                   | ON  | -   | -   | -   | -   | -   | -                  | xx0xx3 |

| OFF                  | ON  | -   | -   | -   | -   | -   | -                  | xx4xx7 |

| ON                   | OFF | -   | -   | -   | -   | -   | -                  | xx8xxB |

#### Input/Output mode selection

The 24 channels of digital I/O on the UEI-817 are divided into three, byte-wide ports. Each port can be configured as digital input or digital output. When selected all eight channels of that port are configured as either digital inputs or digital outputs. Factory-default configuration for all three ports is digital output

| Port   | Mode   | Jumper settings |  |

|--------|--------|-----------------|--|

| Port 0 | Input  | W6 open         |  |

|        | Output | W6 AB           |  |

| Port 1 | Input  | W7 open         |  |

|        | Output | W7 AB           |  |

| Port 2 | Input  | W8 open         |  |

|        | Output | W8 AB           |  |

#### Interrupt request line selection

The UEI-817 allows to generate hardware interrupt when the digital input data changes on any channel of the port 0. The UEI-817 is linked to the interrupt structure of the PC and provides following interrupt request line selection : IRQ2, IRQ3, IRQ4, IRQ5, IRQ6, IRQ7. Factory-default configuration is IRQ2. Use W9 jumper to select desired interrupt line.

| IRQ line | Jumper settings |  |  |

|----------|-----------------|--|--|

| None     | W9 open         |  |  |

| IRQ2     | W9 MN           |  |  |

| IRQ3     | W9 KL           |  |  |

| IRQ4     | W9 HJ           |  |  |

| IRQ5     | W9 EF           |  |  |

| IRQ6     | W9 CD           |  |  |

| IRQ7     | W9 AB           |  |  |

#### Input latch selection

There are two ways to latch digital input data for the ports 0..2 : data can be latched by the READ DATA strobe from the host PC(normal operation) or by the TTL input latch source (port 0/channel 0 for the port 0, port 0/channel 1 for the port 1 and port 0/channel 2 for the port 2). Factory-default configuration is a normal operation. Use W1/W2/W3 jumpers to select input latch mode.

| Port   | Latch Mode              | Jumper settings |  |

|--------|-------------------------|-----------------|--|

| Port 0 | TTL Strobe on Channel 0 | W1 AB           |  |

|        | Normal operation        | W1 BC           |  |

| Port 1 | TTL Strobe on Channel 1 | W2 AB           |  |

|        | Normal operation        | W2 BC           |  |

| Port 2 | TTL Strobe on Channel 2 | W3 AB           |  |

|        | Normal operation        | W3 BC           |  |

#### Input change-of-state latch for the port 0 selection

During the normal operation, digital input data from the port 0 is latched by the READ DATA strobe from the host PC. If you select a change-of-state latch for the port 0, every time the digital input data changes, the data is latched in the input register by the interrupt request line. Factory-default configuration is a normal operation. Use 4 jumper to select input change-of-state latch mode.

| Port   | Latch Mode       | Jumper settings |  |  |

|--------|------------------|-----------------|--|--|

| Port 0 | Change-of-state  | W4 AB           |  |  |

|        | Normal operation | W4 BC           |  |  |

### J1 Connector Pin Assignments

| Pin | Function              | Pin | Function       |

|-----|-----------------------|-----|----------------|

| 1   | Port 2 / DIO Channel7 | 2   | Digital Ground |

| 3   | Port 2 / DIO Channel6 | 4   | Digital Ground |

| 5   | Port 2 / DIO Channel5 | 6   | Digital Ground |

| 7   | Port 2 / DIO Channel7 | 8   | Digital Ground |

| 9   | Port 2 / DIO Channel3 | 10  | Digital Ground |

| 11  | Port 2 / DIO Channel2 | 12  | Digital Ground |

| 13  | Port 2 / DIO Channel1 | 14  | Digital Ground |

| 15  | Port 2 / DIO Channel0 | 16  | Digital Ground |

| 17  | Port 1 / DIO Channel7 | 18  | Digital Ground |

| 19  | Port 1 / DIO Channel6 | 20  | Digital Ground |

| 21  | Port 1 / DIO Channel5 | 22  | Digital Ground |

| 23  | Port 1 / DIO Channel7 | 24  | Digital Ground |

| 25  | Port 1 / DIO Channel3 | 26  | Digital Ground |

| 27  | Port 1 / DIO Channel2 | 28  | Digital Ground |

| 29  | Port 1 / DIO Channel1 | 30  | Digital Ground |

| 31  | Port 1 / DIO Channel0 | 32  | Digital Ground |

| 33  | Port 0 / DIO Channel7 | 34  | Digital Ground |

| 35  | Port 0 / DIO Channel6 | 36  | Digital Ground |

| 37  | Port 0 / DIO Channel5 | 38  | Digital Ground |

| 39  | Port 0 / DIO Channel7 | 40  | Digital Ground |

| 41  | Port 0 / DIO Channel3 | 42  | Digital Ground |

| 43  | Port 0 / DIO Channel2 | 44  | Digital Ground |

| 45  | Port 0 / DIO Channel1 | 46  | Digital Ground |

| 47  | Port 0 / DIO Channel0 | 48  | Digital Ground |

| 49  | +5V DC(250mA)         | 50  | Digital Ground |

#### The J1 connector of the UEI-817 board is identical to the J1 connector of the RTI-817 board

#### I/O memory map

The UEI-817 is mapped into the computer's I/O memory map as four consecutive bytes. Each byte has a pre-assigned function and the four bytes taken as a whole represent the I/O map of the UEI-817. The first byte (base address+0) is used as interrupt enable/clear byte. Three other locations are assigned to the I/O ports 0, 1 and 2.

| Address | MSB |   |   |   |   |   |   | LSB | Description                          |

|---------|-----|---|---|---|---|---|---|-----|--------------------------------------|

|         |     |   |   |   |   |   |   |     |                                      |

| BASE+3  | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   | Port 2 Digital Out (WRITE)/          |

|         |     |   |   |   |   |   |   |     | Port 2 Digital In/Read-back (READ)   |

| BASE+2  | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   | Port 1 Digital Out (WRITE)/          |

|         |     |   |   |   |   |   |   |     | Port 1 Digital In/Read-back (READ)   |

| BASE+1  | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   | Port 0 Digital Out (WRITE)/          |

|         |     |   |   |   |   |   |   |     | Port 0 Digital In/Read-back (READ)   |

| BASE+0  | Х   | Х | х | х | х | Х | Х | IS  | Interrupt Enable(0)/Disable(1) WRITE |

|         |     |   |   |   |   |   |   |     | Interrupt clear (READ)               |